目次[隠す]

- 1. 書式

- 2. アーキテクチャ名

- 3. 各種宣言

- 3-1. 宣言の種類

- 4. 本体

- 4-1. 組み合わせ回路

- 4-2. 順序回路

- 4-3. 下位モジュール呼び出し

- 5. まとめ

- 6. 掲載ソースの動作確認

- パッケージ読み込み

- エンティティ(Entity)宣言

に続いて

- アーキテクチャ(Architecture)

を記述します。

エンティティ部は外部からの見た目を定義しています。

一方で、このアーキテクチャ部にはコンポーネントの動作を記述します。

書式

アーキテクチャ部は次のように記述します。

- architecture宣言とbeginの間に各種の宣言を書き

- beginの後に処理内容を記述する

アーキテクチャ名

アーキテクチャ名は任意に決められます。

好きなように名付けて構わないんですが、論理合成を前提とした回路を記述する場合はRTLとするケースが多いです。僕は内容に応じてbehavior, RTL, Simulationを使っています。

論理合成対象はRLT、シミュレーションに使うテストベンチはSimulationという感じです。

一つのエンティティに対して複数のarchitectureを持つこともできます。その場合、どのアーキテクチャの動作をさせるかはアーキテクチャ名で区別されます。

各種宣言

宣言の種類

- Signal (信号配線)

回路の配線にあたります。 - Constant (定数)

定数です。動作途中で値が変更されることがないので、固定値を記述するのによく使います。 - Component (下位モジュール)

下位モジュールを接続するために、その下位モジュールのエンティティ宣言に似たものを記述します。その下位モジュールがどういうポート構成になっているかがわかります。 - Variable (変数)

変数です。論理合成対象ではありません。テストベンチの記述やFunction文周辺などで使います。

各種宣言のソースの例

- Signal, Constant, Valiable にはデータタイプの指定が必要です (std_logicやintegerなど)

- 上記の例では、コンスタント(Constant)宣言と同時に値を代入しています

- シグナル(Signal)も宣言時に初期値を代入できます。ですが、僕は初期リセットで値を入れるので、普段はここに代入の記述はしません。

本体

この部分に処理内容を書きます。

具体的には

- 組み合わせ回路

- 順序回路

- 下位コンポーネントの呼び出し

などです。以下、簡単な説明と記述例です。

組み合わせ回路

組み合わせ回路は、クロックと同期せずに値が変化します。(非同期回路という)

組み合わせ回路には一行で書ける簡単な回路や、process文で記述する複雑な回路もあります。

順序回路

フリップフロップ(FF)やラッチを含む回路です。基本的にクロックに同期して動作します。

組み合わせ回路と同様にprocess文で記述しますが、センシティビティリスト(process文の直後のカッコ内の信号)が異なります。

順序回路では、センシティビティリストにクロックが含まれます。

非同期の順序回路ではクロック以外の信号も含まれます(例えば非同期リセット回路のリセット信号)。

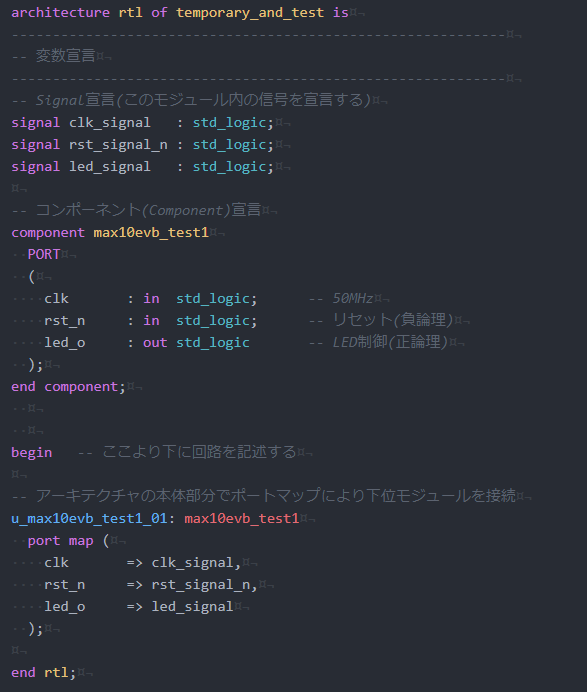

下位モジュール呼び出し

現在のモジュールの下に別のモジュールを接続する記述です。

以下の例ではmax10evb_test1モジュールを呼び出して接続しています。

まとめ

- VHDLの記述は次の要素で構成されます

- パッケージ呼び出し

- エンティティ(Entity)

- アーキテクチャ(Architecture)

- アーキテクチャには任意のアーキテクチャ名をつけます

(論理合成対象ならRTLとすることが多い) - アーキテクチャは、各種宣言、本体の順に記述します

- 各種宣言では以下のものを宣言できます

- Signal

- Constant

- Component

- Variable

- 本体では以下のような回路を記述します

- 組み合わせ回路

- 順序回路

- 下位モジュール呼び出し

掲載ソースの動作確認

掲載のソースコードは、Intel(Altera)のQuartus Prime 18.1 Lite Editionで文法チェックしています。

Xilinxでは確認していないので、もしVivadoやISEでコンパイルエラーが出ていたらコメントいただけるとうれしいです。

テキストエディタは、Notepad++とAtomを使っています。

コメントを残す