2022年にVitis HLSでIP化に失敗する対策

Vitis HLS で Export RTL 時にエラーが出る問題 高位合成で作成した回路をIP化しようとすると、エラーが発生してIPが作成できない問題が発生しました。(2022年問題?) ‘22012116...

FPGA

FPGAVitis HLS で Export RTL 時にエラーが出る問題 高位合成で作成した回路をIP化しようとすると、エラーが発生してIPが作成できない問題が発生しました。(2022年問題?) ‘22012116...

FPGA

FPGAこの記事はXilinxの Vitis HLSユーザーガイド(UG1399(v2021.1)) の「第4章 Vitis HLSプロセスの概要」と「第17章 インターフェイスの定義」を参考にして書いています。 インターフェー...

C言語

C言語この記事の内容 Zynq でタイマー割り込みのテストプログラムの main 関数の内容のメモ。 このテストプログラムはFPGA設計大全第2版の第5章に載っています。RGB LED の色を一定時間ごとに変化させるプログラム...

C言語

C言語この記事の内容 Zynq 割り込み処理登録を行う関数について。 Zynq の CPU でタイマー割り込みによって RGB LED の色を切り替えていく例が、FPGA設計大全第2版の第5章に載っています。C のソースコード...

C言語

C言語この記事の内容 Zynq 割り込みコントローラのドライバ初期化関数について。 FPGA設計大全第2版の第5章に 「Zynq の CPU でタイマー割り込みを使って 3色 LED の色を切り替えるテストコード」があります。...

C言語

C言語この記事の内容 Zynq タイマー割り込みの関数について。 FPGA設計大全第2版の第5章に、 Zynq の CPU を使ってタイマー割り込みで RGB LED の色を切り替えていく例が載っています。その C言語のコード...

FPGA

FPGAはじめに 目的 デバッグ途中でつまずいたときに「環境のせいじゃないよ」と切り分けられるように、事前にサンプルプロジェクトの「Simple Hello World」を動かしてみます。 現時点での最終目的は「ADCで温度読み...

FPGA

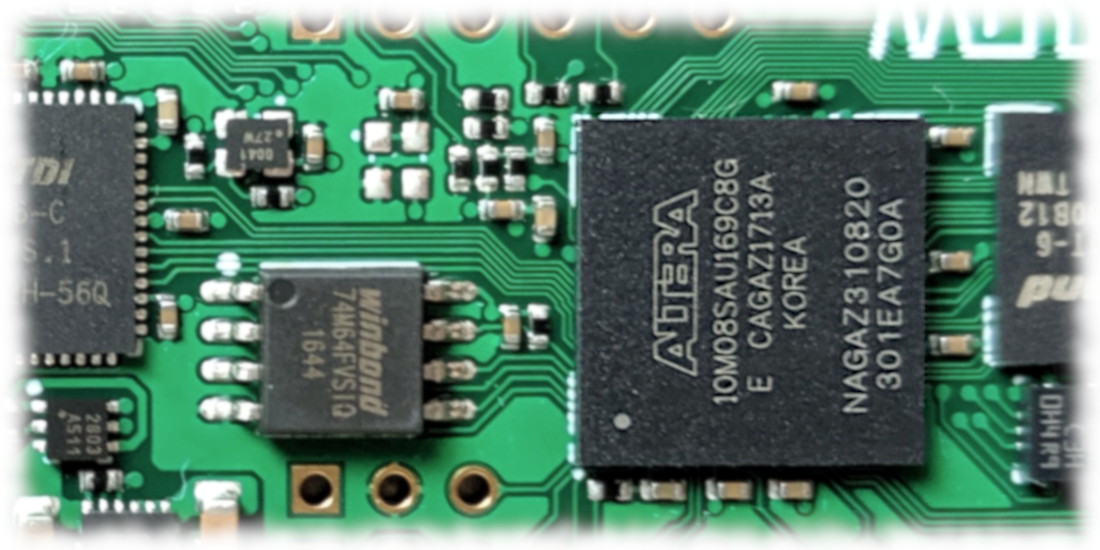

FPGA概要 Intel MAX10 FPGAにはADC(アナログ・デジタル・コンバータ)が内蔵されていて、外部電圧と内部温度を読み取ることができます。 前回の記事では、MAX10 FPGAの評価ボードを使ってFPGA内部の温度...

FPGA

FPGAMAX 10はADC (アナログ・デジタル・コンバーター)を内蔵しています。Intelの公式動画に沿って内部温度を読み取ってみましょう。 この記事を読むとこんなことがわかるようになります。 MAX 10のADCの使い方が...

MAX10

MAX10MAX10 Device Overviewの内容を整理しました。Overviewとは別にデータシートもあります。 目次 1. 特徴 2. 型番の詳細 (発注情報, Ordering Information) 2-1. 型...