ノイズ試験におけるEMI(エミッション)で問題になることがあるデジタル回路の高調波について解説します。

- 矩形波の周波数成分と包絡線

- 共振によるノイズ、EMI対策部品での対策

- LTspiceでのFFT波形確認

の3つに分けて解説します。この記事は「共振によるノイズ、EMI対策部品での対策」です。

目次

- 1. 共振時のスペクトラム

- 2. 共振と信号の立ち上がり速度の関係

- 2-1. 共振が起こるリスクを下げる

- 2-2. 配線長10cmのときの立ち上がり時間を計算

- 2-3. シミュレーションで波形を確認

- 3. フェライトビーズを使ったノイズ対策

- 3-1. シミュレーション条件

- 3-2. シミュレーション結果

- 4. 共振のコントロール

- 4-1. 共振が最大になる条件

- 4-2. 反射係数

- 4-3. そのほかの共振を抑える方法

- 5. まとめ

- 5-1. 共振について

- 5-2. ノイズ対策

- 5-3. 共振を抑える方法

- 5-3. 補足:シミュレーション

共振時のスペクトラム

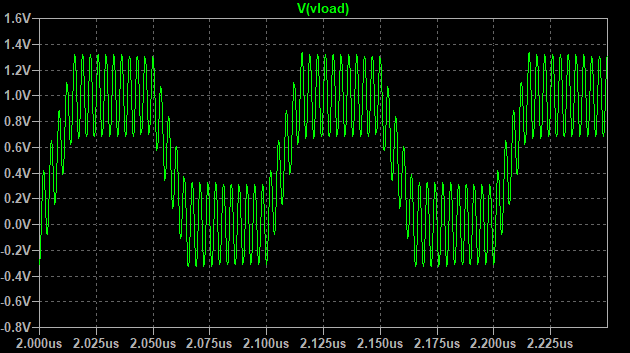

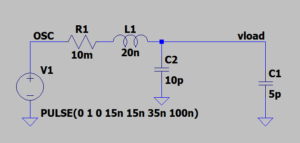

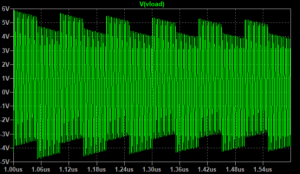

リンギングが発生している矩形波の、時間領域と周波数領域の波形です。周波数領域で確認すると、300 MHz付近にピークが存在します。リンギングはEMIへの影響だけではなく、信号品質にも影響を及ぼします。

この記事では、リンギングや共振を抑える方法を検討していきます。

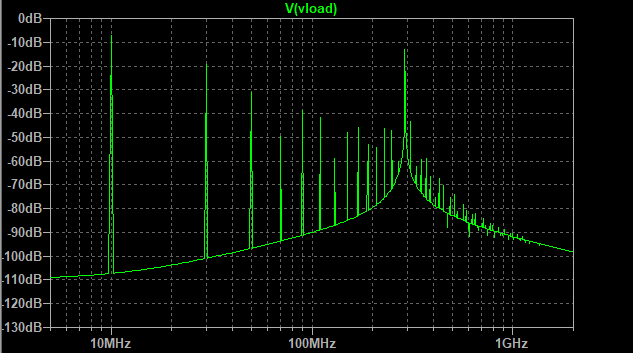

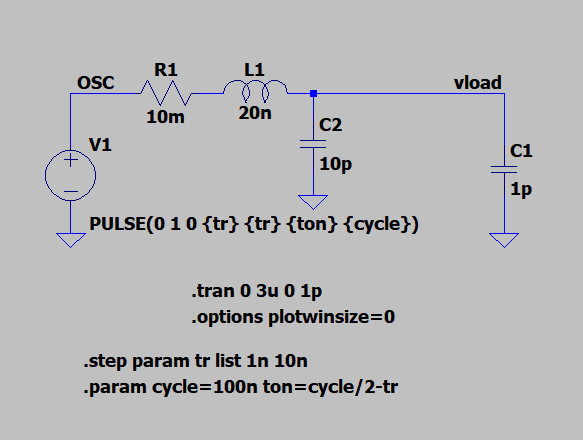

なお、この波形のシミュレーションに使用した回路はこちら(↓)です。

共振と信号の立ち上がり速度の関係

共振が起こるリスクを下げる

配線長L ≪ 信号の波長/4

この関係式のように、信号に含まれる周波数成分の波長λの1/4が配線長Lよりも十分に長ければ、共振が問題になる可能性は低くなります。

10cmの配線を例にすると、λ/4 = 10 cm、つまりλ = 40 cmよりも信号の波長が十分に長ければ共振のリスクは低いと考えられます。

配線長10cmのときの立ち上がり時間を計算

波長が40cm (λ/4=10cm) である信号に相当する立ち上がり時間を計算してみます。

波長から周波数を求める

基板の比誘電率を4と仮定すると、波長が40cmである波の周波数は次の式のように374.7 MHzとなります。

\[\frac{c}{\sqrt{4}}\cdot\frac{1}{0.4} = 374.7 \mathrm{(MHz)}\]

ここでは次の2つの式を使っています。

上側の式は、基板上の信号は真空中よりも伝搬速度が遅くなることを表しています。

- \[信号伝搬速度 = \frac{真空中の光速}{\sqrt{実効比誘電率}}\]

- \[v=f\lambda\]

立ち上がり時間を求める

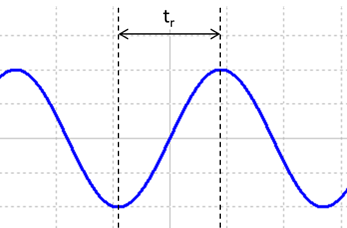

次に374.7 MHzの正弦波を考えて、立ち上がり時間を確認します。

ざっくりですが、立ち上がり時間は下の図のように正弦波の1/2周期と考えられるので、この場合は約1.3nsとみなせます。

計算のまとめ

波長40cmに相当する立ち上がり時間は、およそ1.3nsとわかりました。

配線長10cmの伝送線路(配線パターン)おいて、信号の立ち上がり(立ち下がり)時間を1.3nsよりも十分に長くできれば共振のリスクを抑えることができます。

シミュレーションで波形を確認

立ち上がり時間trを変えて、配線長10cm相当のRLC素子通過後の波形を比較しました。

「高調波と包絡線」の記事では抵抗負荷にしていましたが、ここではCMOS ICを想定して容量負荷に変更しました。

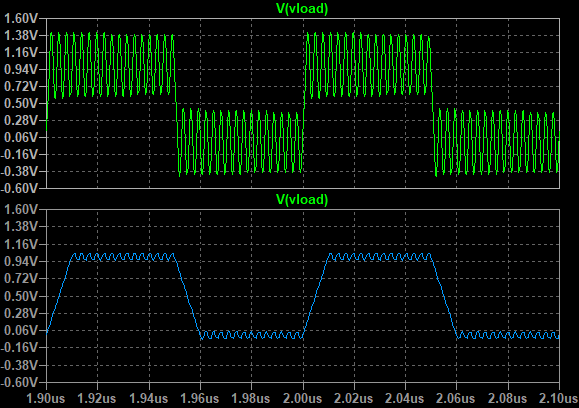

- tr = 1 nsのときは、波形は常に振動していて信号波形として使うことは難しそうです。

- tr = 10 nsでは振幅に対して波打ちは少なく、矩形波(台形波)としては問題なさそうです。

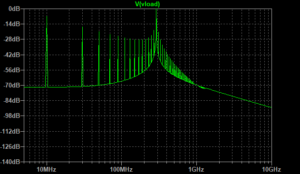

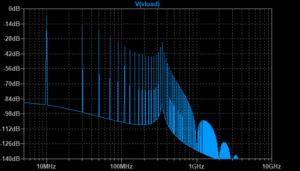

FFT結果です。ノイズのレベルや、周波数が高い領域の包絡線に違いがあります。

フェライトビーズを使ったノイズ対策

立ち上がり時間が1nsの回路にフェライトビーズを追加して、ノイズが軽減できることを確認してみます。

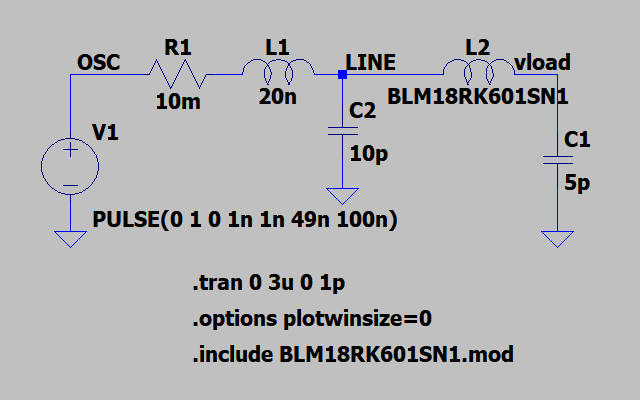

シミュレーション条件

先ほどの回路から負荷容量の値を変えました。条件はこちらです。

- 負荷容量 CL=5 pF

- 配線長Lは10cmを想定

R=10 mΩ

L=20 nH

C=10 pF - フェライトビーズは村田製作所製のBLM18RK601SN1

フェライトビーズはメーカーホームページでSPICEモデルが公開されているので、ダウンロードして使用しました。

次の回路でシミュレーションします。

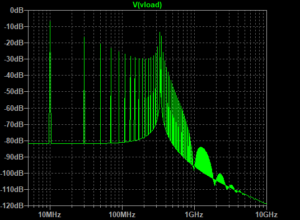

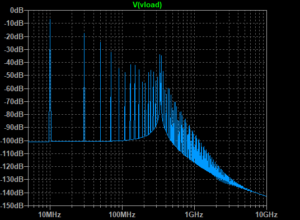

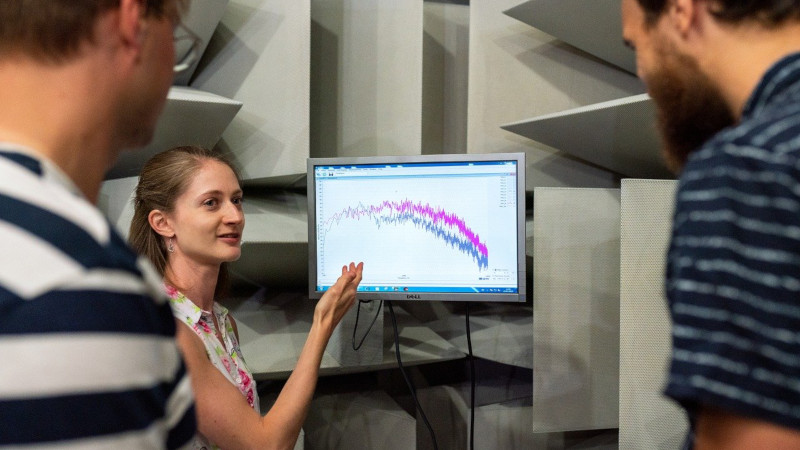

シミュレーション結果

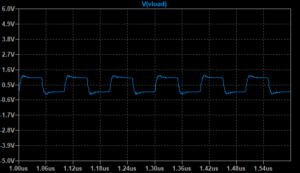

まず、時間軸波形です。2つのグラフのスケールは合わせてあります。

- 緑色:フェライトビーズなし

- 青色:フェライトビーズあり

- フェライトビーズがない状態では、共振が発生して振幅が大きくなっています。本来の波形がわかりません。

- フェライトビーズを追加すると、(特定の)高周波成分が除去され、矩形波が確認できました。

続いて、上の時間軸波形をFFTした結果です。

- フェライトビーズ追加前は290 MHz付近に大きなピークがあります。

- フェライトビーズ追加後は、ピークだけでなく全体のベイズレベルが下がっています。

このように、フェライトビーズによって共振によるノイズを抑え、ノイズレベルを下げられることを確認しました。

共振のコントロール

共振が最大になる条件

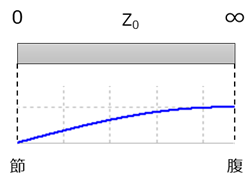

線路の一方が短絡、もう一方が開放になっているときに λ/4共振となり 、共振が最大になります。 短絡側が節、開放側が腹になっています。

反射係数

伝送線路の反射係数Γは次の式で表されます。

\[\Gamma = \frac{R-Z_0}{R+Z_0}\]

ここで、 Z0:線路の特性インピーダンス、R:両終端インピーダンス です。

共振を小さくするためには、反射係数を0にすればよいので、Γを0に近づけるためには、RをZ0に近づけるとよいことがわかります。

線路の特性インピーダンスが50 Ωの場合は、50 Ωで終端すると反射係数が0になります。そうすると、線路端での反射がなくなり、共振もなくなります。

そのほかの共振を抑える方法

具体的なノウハウというよりは一般的な方法ですが、損失を線路に損失をもたせることで共振を減衰させることができます。

- 線路全体に損失をもたせる

→ 誘電体材料を使用する - 部分的に抵抗を挿入する

→ スナバー回路(RとCの直列回路)を挿入する

まとめ

共振について

- 共振により高周波ノイズが発生し、スペクトラムにピークが現れる

- 信号に含まれる成分の波長の1/4の長さに対して、線路帳が十分に短ければ、共振が発生する可能性は低い (配線長L ≪ 信号の波長/4)

ノイズ対策

- ノイズ対策部品として適切なフェライトビーズを使用すると、共振による不要な周波数を除去し、ノイズ性能・波形品質を改善できる

共振を抑える方法

- 共振を抑えるには、終端インピーダンスを線路の特性インピーダンスに合わせればよい

- インピーダンスを合わせられない場合は、スナバー回路などで損失を持たせて共振を減衰させる方法がある

補足:シミュレーション

ここでの検討はすべてシミュレーションのため、実機での動作と異なることがあります。(実機の条件に近づけるような配慮はしていません。)

実機でノイズ問題が発生している場合は、発生箇所の特定→対策の順で進めていくのがよいと思います。対策方法もいろいろありますので、状況に応じて最適な方法を選択する必要があります。

コメントを残す