この記事はXilinxの Vitis HLSユーザーガイド(UG1399(v2021.1)) の「第4章 Vitis HLSプロセスの概要」と「第17章 インターフェイスの定義」を参考にして書いています。

目次

インターフェースについて

Vitis HLSで作成するデザインの最上位関数の引数は、インターフェースおよびポートとして合成されます。インターフェースは、複数の信号をグループ化したものです。

インターフェースで使用するプロトコルはVitis HLSツールが自動で決定するほか、ユーザーが手動で割り当てることもできます。

以下の要素によってインターフェースが定義されます。

- 最上位関数のデータ型および方向

- ターゲットフロー

- デフォルトのインターフェースコンフィギュレーション (config_interfaceで指定)

- INTERFACEプラグマまたは指示子

最後のINTERFACEプラグマまたは指示子は、ユーザーが手動でプロトコルを割り当てるための方法です。

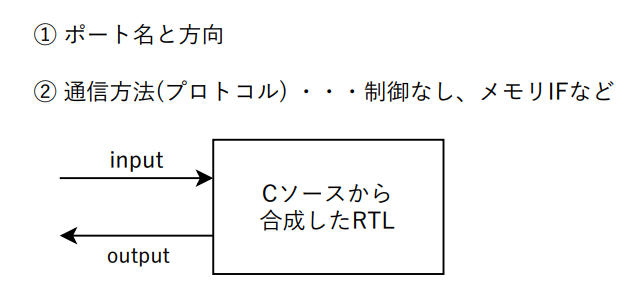

インターフェースの3つの要素

- 入出力チャンネルを定義

- ポートプロトコルを定義

- 実行制御機構(実行制御スキーム)を定義

入出力チャンネル

HLSによって合成するデザインの入出力チャンネル(ポート)を決める

ポートプロトコル

チャンネルで使用するプロトコルを指定する

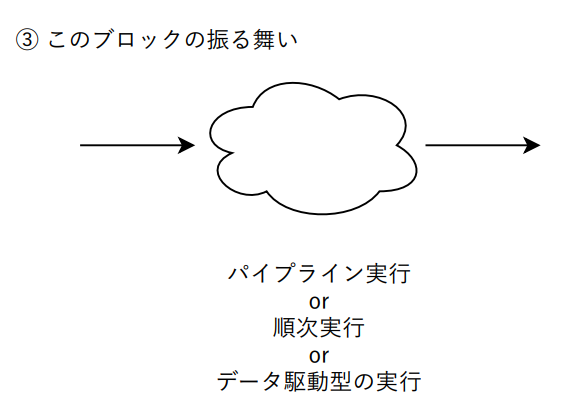

制御スキーム

デザインブロックがどのように動作するかを指定する。順次実行で動作するかパイプライン実行で動作するかなど。

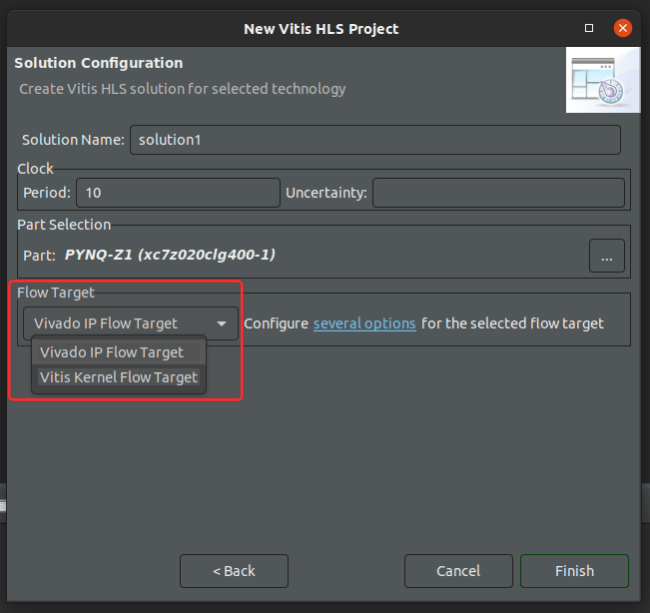

ターゲットフローの概要と選択

HLSでデザインを正しく動作させるためには、インターフェースの選択と設定がポイントとなります。Vitisツールでターゲットフローを選択できることで、インターフェースの選択・設定の手順が簡素化されています。

Vitis HLSではターゲットフローを2つのフローから選択できます。ツールのデフォルトはVivado IPフローです。

フロー比較

| Vivado IPフロー (デフォルト) | Vitisカーネルフロー | |

|---|---|---|

| ターゲット | RLT IPファイル ・Vivado Design Suite ・IPカタログ ・IPIブロックデザイン | アクセラレーション用カーネルオブジェクト(.xo) |

| インターフェース | 関数の引数ごとに割り当て (指示子での指定も可) | AXI規格 (指示子でパラメータ調整可) |

| 自由度 | 高い | 低い (制約が多い) |

| デフォルト実行モード | 順次実行 | パイプライン化された処理 |

インターフェースと実行モードについては後の章で記述。

Vivado IPフロー

Vitis HLSのデフォルトフローです

- 柔軟性が高い(制約は少ない)

→ ユーザーにとっての選択肢は増えるが、IPの統合や管理もユーザーが責任を持つ - 生成したRTL IPファイルは次のデザインの使用する

→ Vivado Design Suite、IPカタログ、IPインテグレーター(IPI)のブロックデザイン - 関数引数のタイプによってインターフェースが決まる (指示子やプラグマで変更可能)

→ 次の表のとおり

Vitisカーネルフロー

- 制約が多い

- アクセラレーションフロー用であり、カーネルオブジェクト(.xo)が生成される

- インターフェースはAXI規格のものが生成される (指示子やプラグマでパラメータ調整が可能)

フローの指定方法

プロジェクト作成時に選択する。

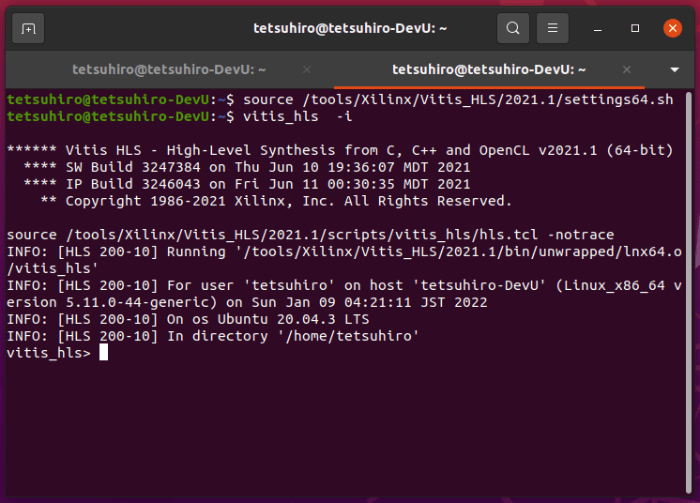

または、次のコマンドでターゲットとするフローを選択できる。

open_solution -flow_target [vitis | vivado]Vitis HLSのインタラクティブモードでコマンドが使用可能。

フローの比較

インターフェースの型

インターフェースは3つの型(パラダイム)をサポートしています。各フローでデザインが外部と通信するための異なるプロトコルがサポートされています。

| 型 | Vivado IPフロー | Vitisカーネルフロー |

|---|---|---|

| メモリ | ap_memory, BRAM, m_axi | m_axi |

| ストリーム | ap_fifo, axis | axis |

| レジスタ | ap_none, ap_hs, ap_ack, ap_ovld, ap_vld, x_axilite | s_axilite |

- m_axi:AXI4メモリマップド

- axis:AXI4-Stream

- s_axilite:AXI4-Lite

m_axi, axis, s_axilite はAXI4インターフェースで、VitisカーネルフローはAXI4インターフェースのみをサポートします。Vivado IPフローではAXI4以外のプロトコルも選択できます。

デフォルトのインターフェース

Vivado IPフロー

| C引数タイプ | サポートされる型 | デフォルトの型 | 入力 | 出力 | 入出力 |

|---|---|---|---|---|---|

| スカラー変数 (値渡し) | レジスタ | レジスタ | ap_none | N/A | N/A |

| 配列 | メモリ、ストリーム | メモリ | ap_memory | ap_memory | ap_memory |

| ポインタ | メモリ、ストリーム、レジスタ | レジスタ | ap_none | ap_vld | ap_ovld |

| 参照 | レジスタ | レジスタ | ap_none | ap_vld | ap_vld |

| hls::stream | ストリーム | ストリーム | ap_fifo | ap_fifo | N/A |

ap_none や ap_memory などの詳細は別記事を作成予定です。

Vitisカーネルフロー

| C引数タイプ | 型 | インターフェースプロトコル |

|---|---|---|

| スカラー変数 (値渡し) | レジスタ | s_axilite (AXI4-Lite) |

| 配列 | メモリ | m_axi (AXI4メモリマップド) |

| 配列へのポインタ | メモリ | m_axi |

| スカラーへのポインタ | レジスタ | s_axilite |

| 参照 | レジスタ | s_axilite |

| hls::stream | ストリーム | axis (AXI4-Stream) |

VitisカーネルフローはAXI4インターフェースのみ

実行モード

各フローのデフォルト実行モードは次のとおり。実行モードはブロックレベルの制御プロトコルとして指定されています。

Vivado IPフロー

- 順次実行・・・次のタスク開始前に、前のタスクを完了しておく必要がある

- ap_ctrl_hs ブロック制御プロトコルで指定

Vitisカーネルフロー

- パイプライン実行・・・カーネルの準備ができたらすぐに次の処理が可能で、オーバーラップ実行ができる → スループットが向上する

- ap_ctrl_chain ブロック制御プロトコルで指定

制御プロトコルについて

インターフェースの制御はポートレベル制御とブロックレベル制御の2階層あります。

ポートレベル制御は(ブロック内の)ポート間の関係を定義し、ブロックレベル制御は他のブロックとの関係を定義します。

詳細は別記事を作成予定です。

参考資料

- Xilinx Vitis 高位合成ユーザー ガイド UG1399 (v2021.1)

- FPGAプログラム大全 Xilinx編 第2版

コメントを残す