目次

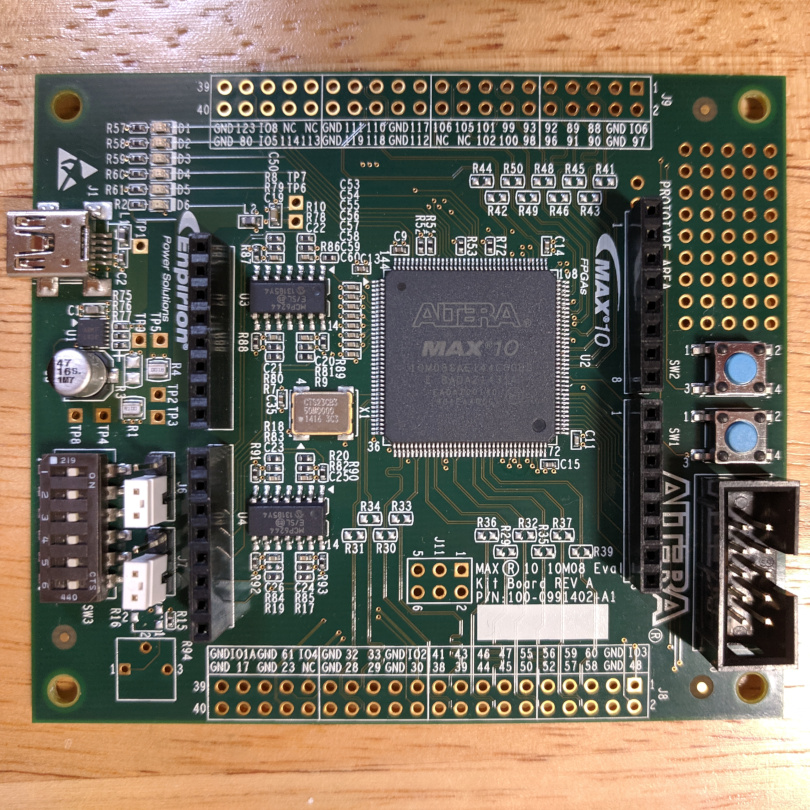

ADCモジュール作成

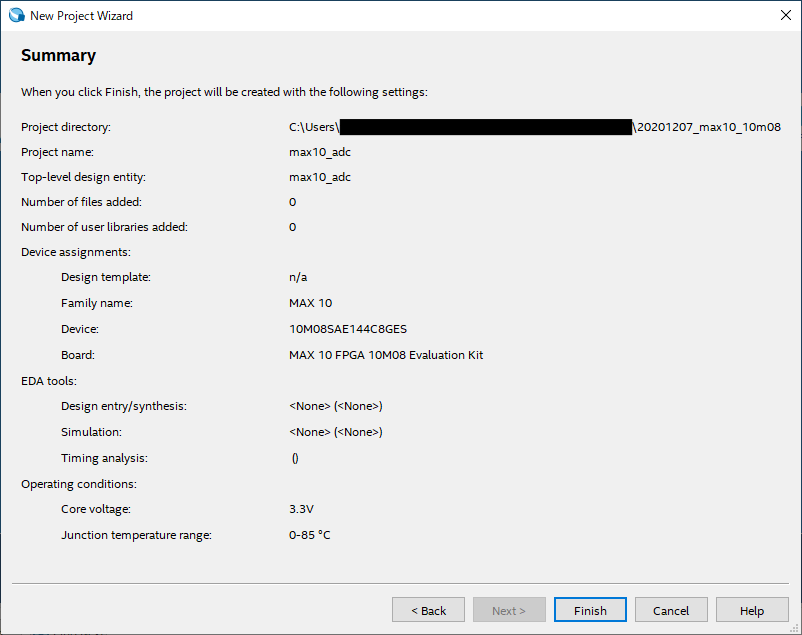

プロジェクト作成

使用するボードやデバイスを選択して、Quartus Primeプロジェクトを作成します。

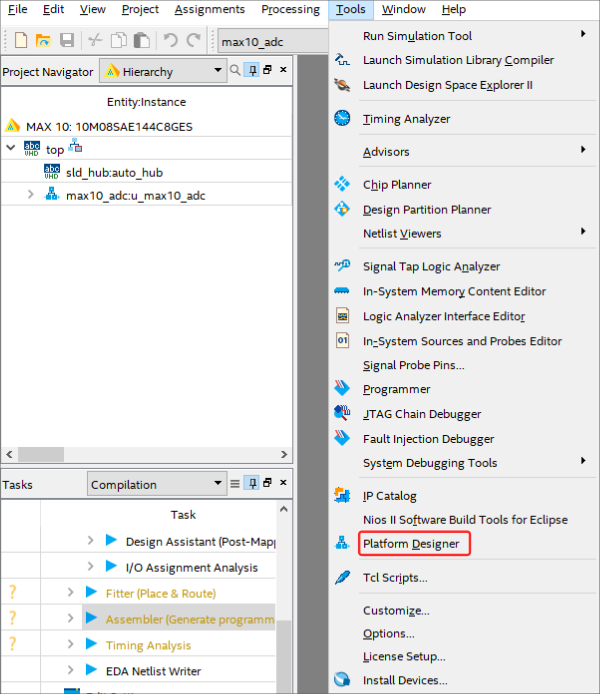

Platform Designerを起動

旧バージョンのQuartusでは「Qsys」。

Platform Designerを使ってペリフェラルを構成します。マイコンを作ると思ってもらうと近い感覚かも。

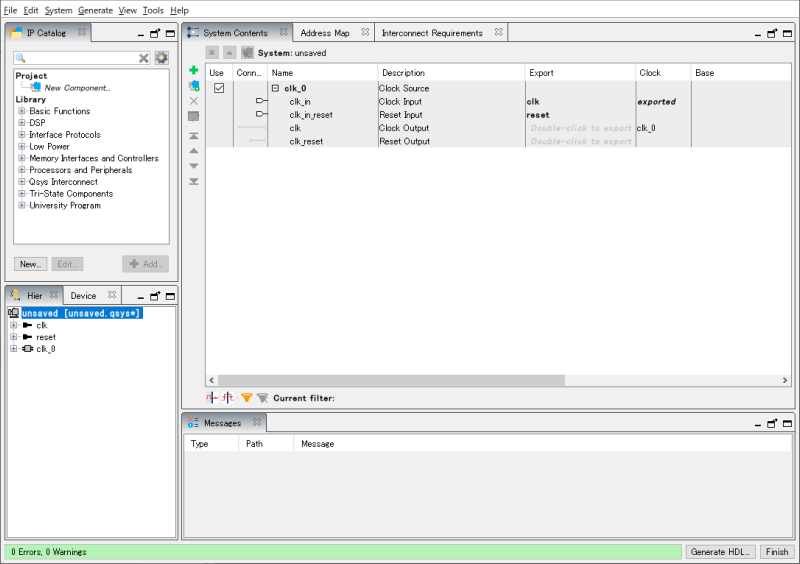

↓Platform Designer起動直後の画面

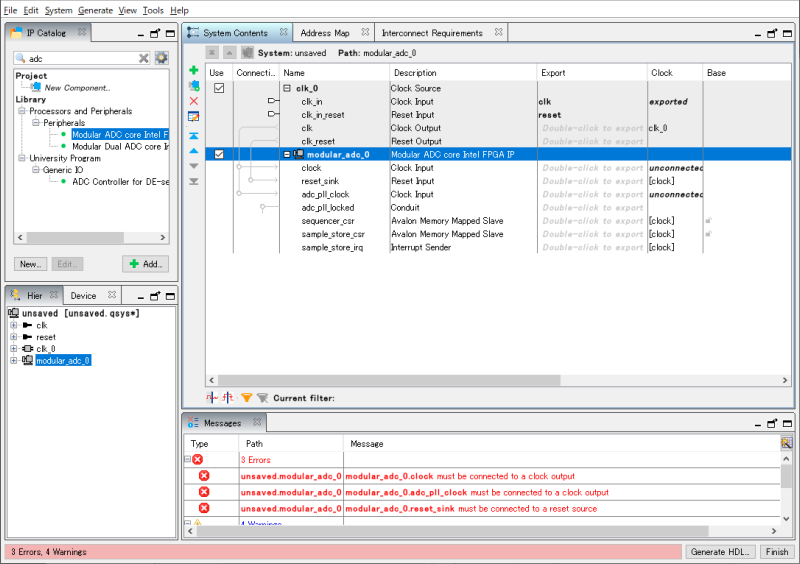

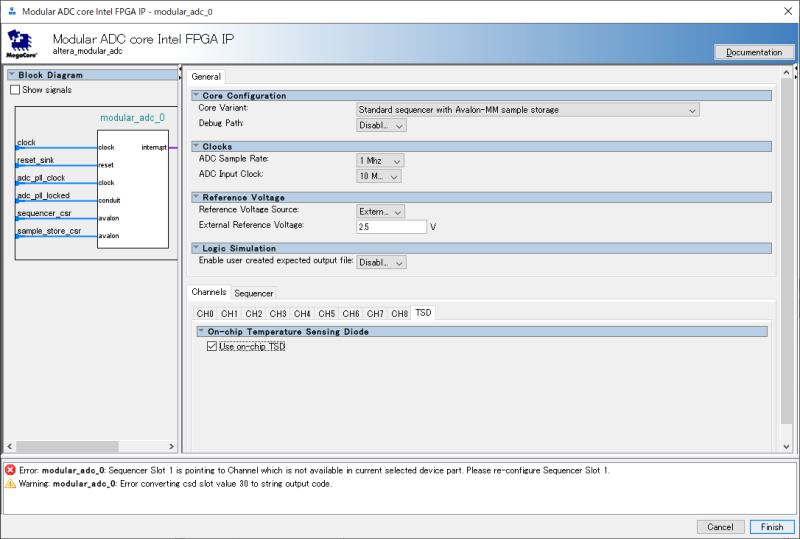

ADCを追加・設定

IP Catalog の検索欄に”ADC”と入力して、Modular ADC core Intel FPGA IP を追加します。

IPの設定変更は2か所。

- チャンネル設定:一番下の”Channels”タブの中で、”TSD”タブを開いて、”Use on-chip TSD”にチェックを入れます。

- シーケンサ設定:”Sequencer”タブで、”Number of slot used”を1に、”Slot 1″をTSDにします。

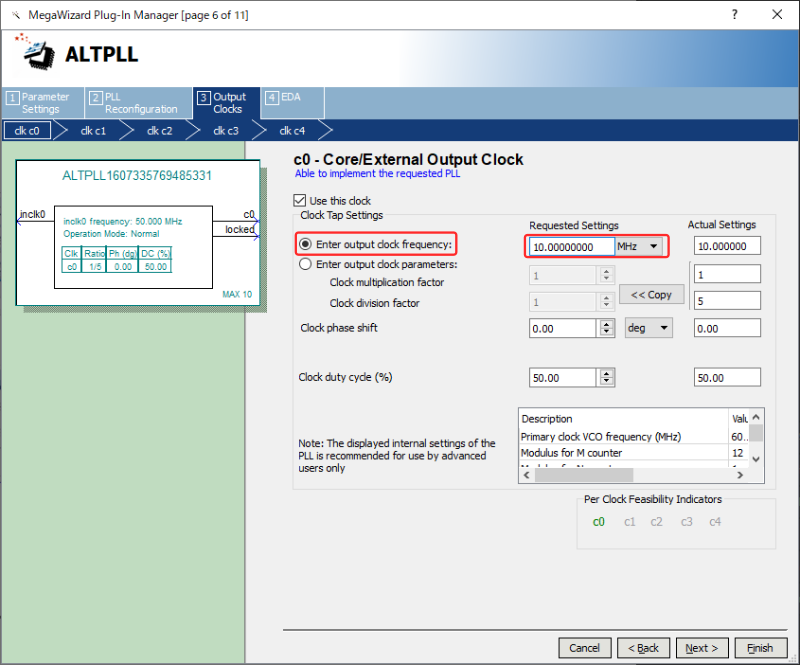

今回は変更しませんが、ADC Input Clockはデフォルトで10MHzになっています。(確認のみ)

PLLを追加・設定

検索欄に”PLL”と入力して、ALTPLL Intel FPGA IPを追加します。

パラメータ変更は3か所。

- 入力クロック周波数をボードに合わせて変更。MAX 10 評価キットの場合は50MHz。

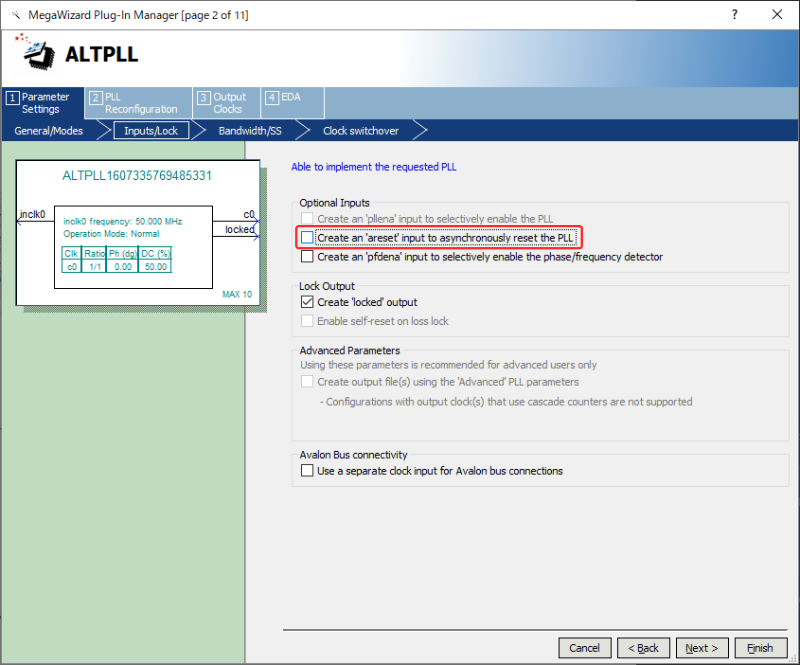

- “Optional Input”の”Create ‘areset’ input …”のチェックを外す。

- ③Output Clocksで、出力クロック周波数を10MHzに設定。

以上を変更したらFinishをクリックして設定を完了しましょう。

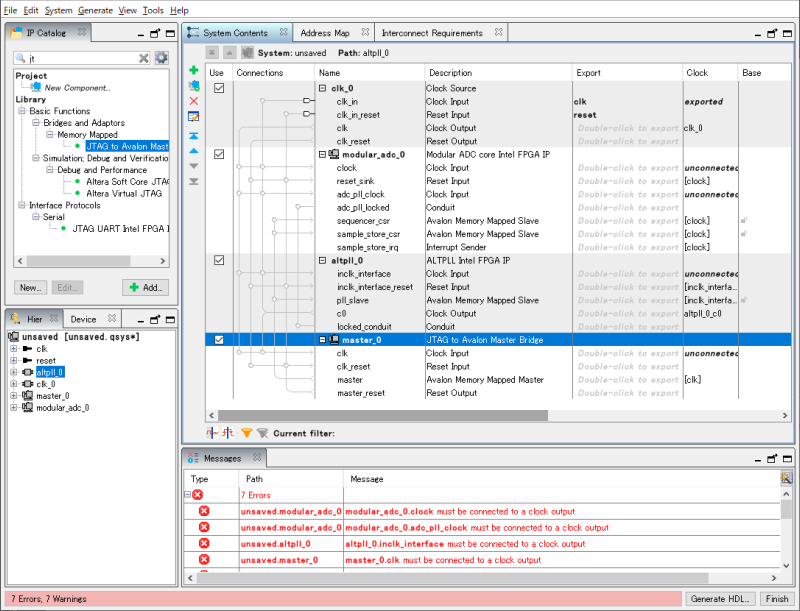

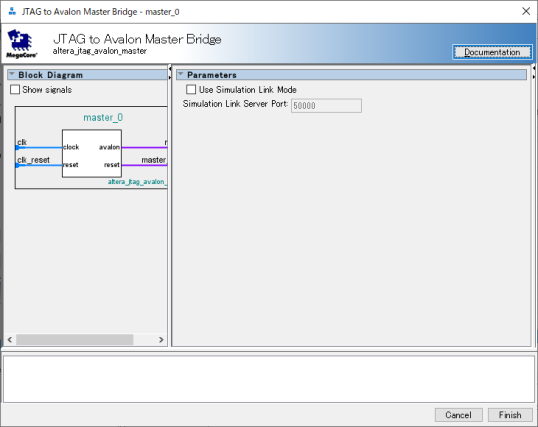

JTAGブリッジを追加

検索欄に”JTAG”と入力して、JTAG to Avalon Master Bridgeを追加します。

設定変更はありません。そのままFinishをクリック。

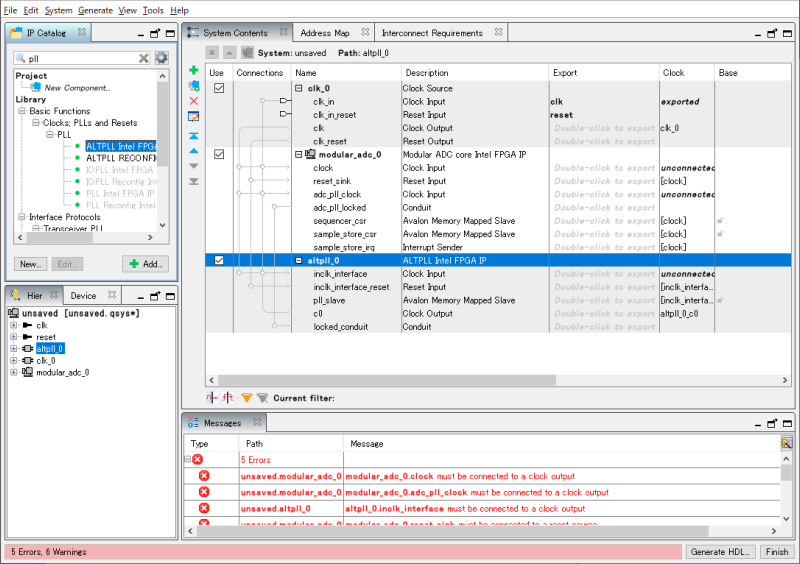

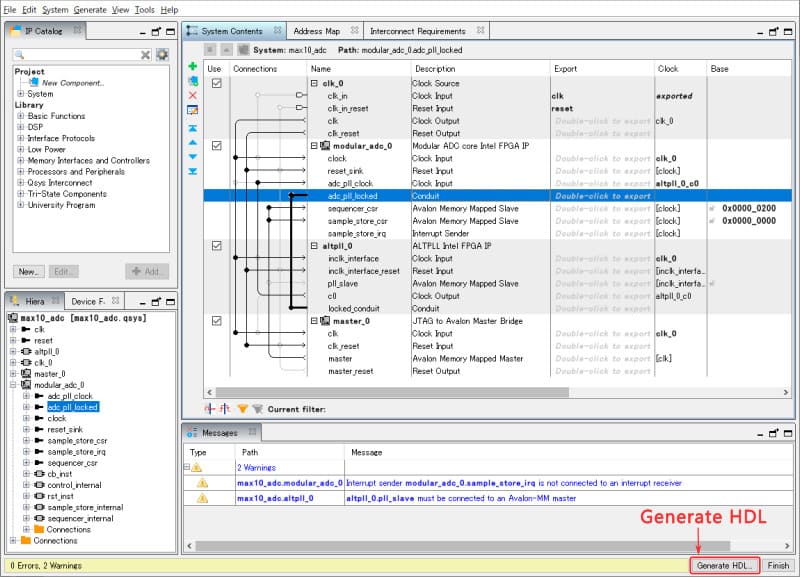

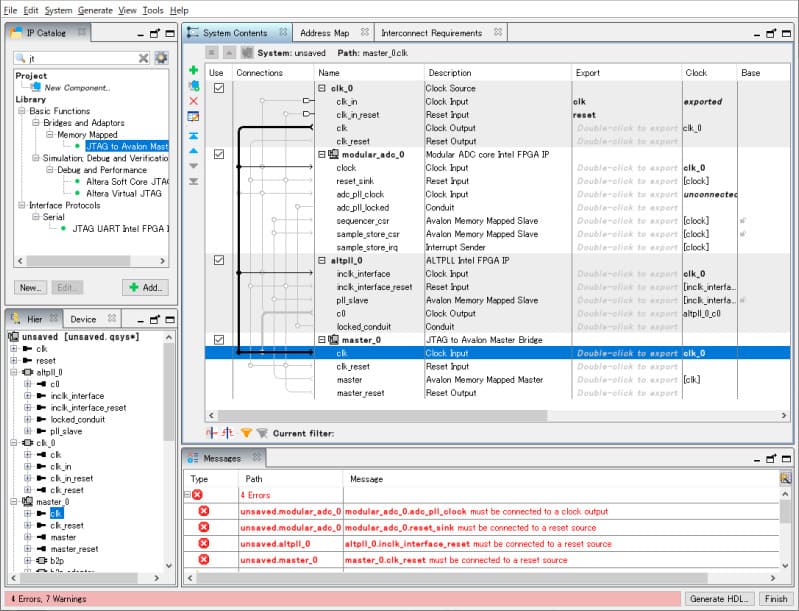

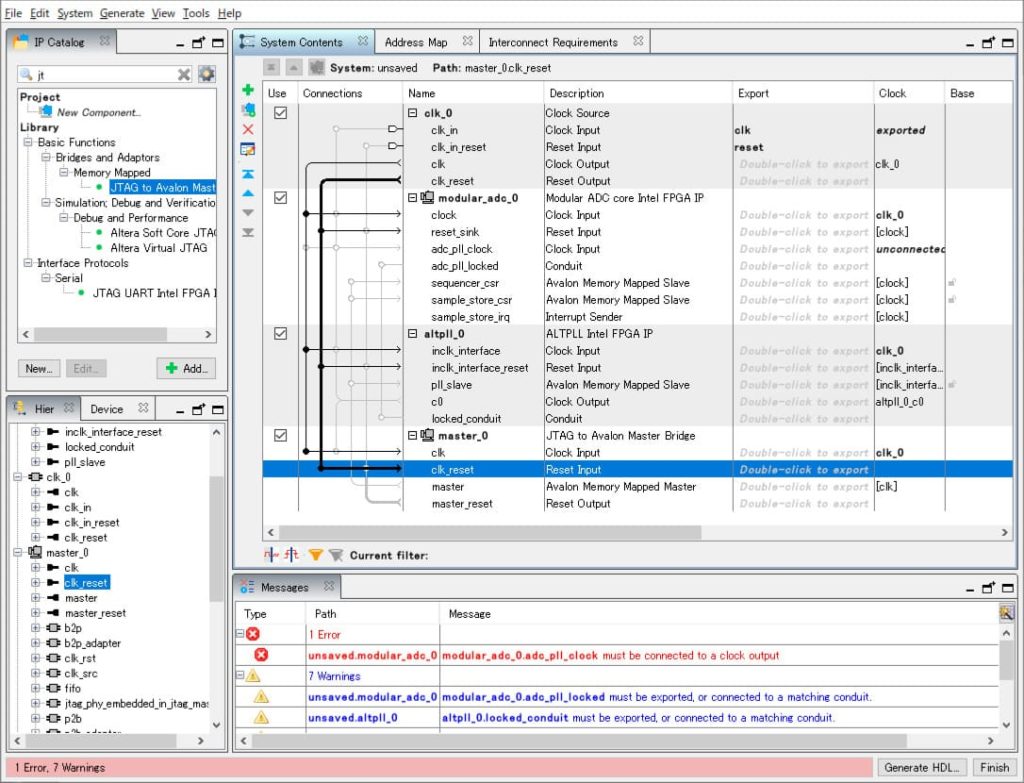

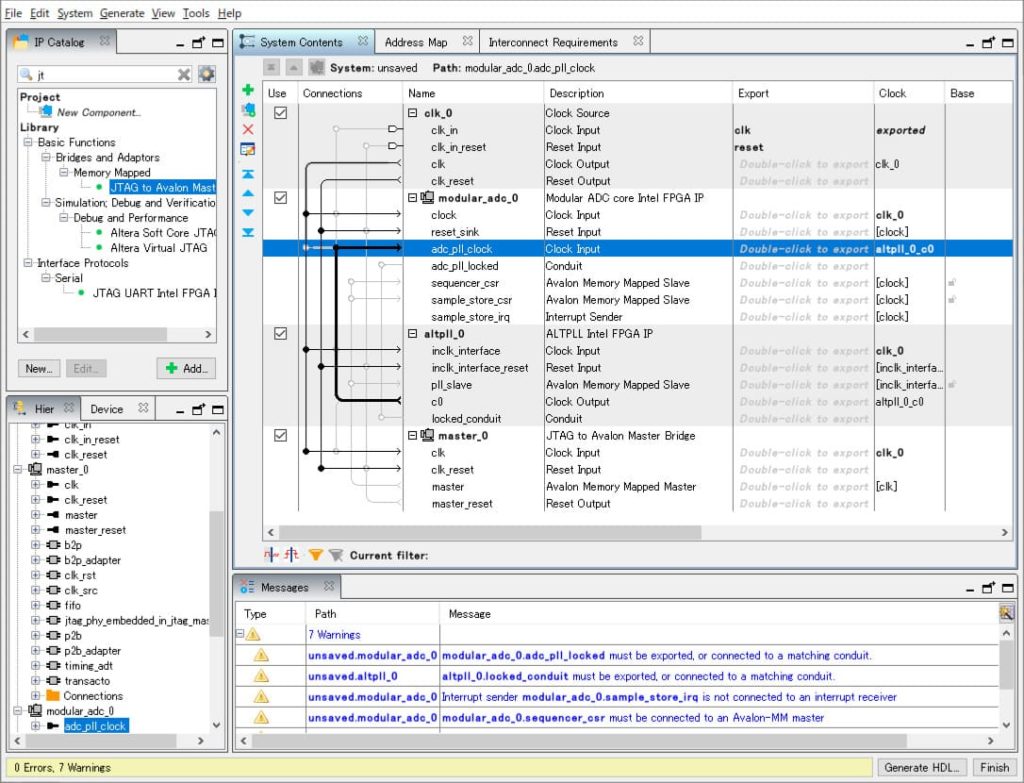

IP間を接続

- CLK接続:3か所

clk0のclk → ADCのclock・PLLのinclk_interface・Masterのclk - Reset接続:3か所

clk0のclk_reset → ADCのreset_sink・PLLのinclk_interface_reset・Masterのclk_reset - PLL CLK接続:1か所

PLLのc0 → ADCのadc_pll_clock - Avalon Bus接続:2か所

Masterのmaster → ADCのsequencer_csrとsample_store_csr - PLL Locked接続:1か所

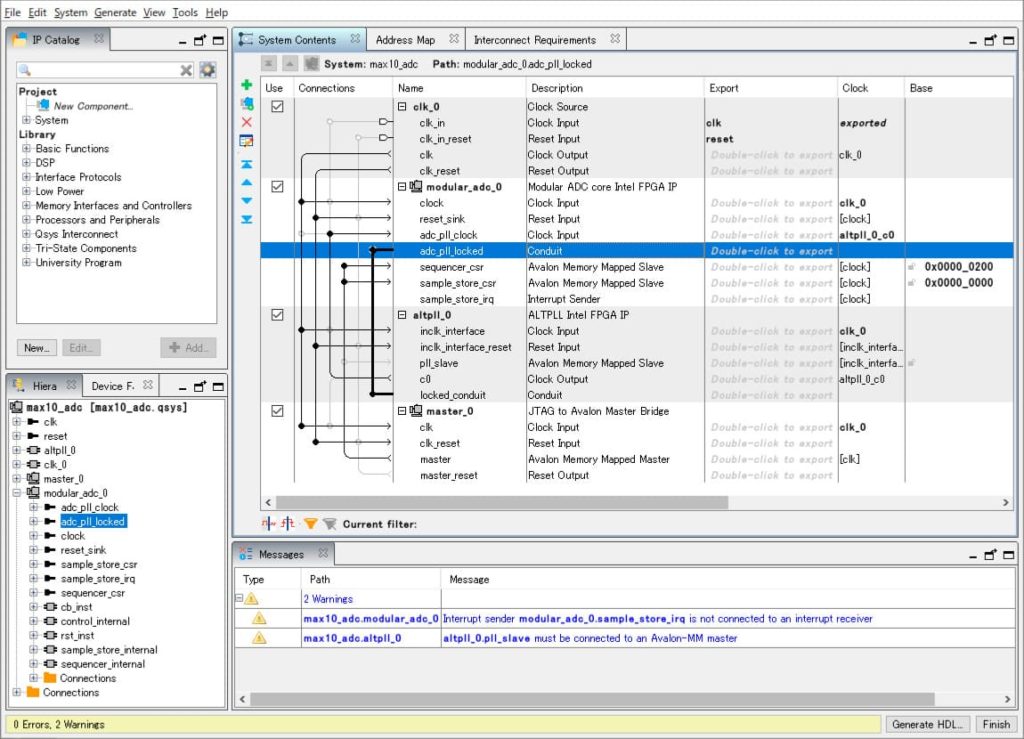

PLLのlocked_conduit → ADCのadc_pll_locked

縦横の線がクロスするところの○(白丸)をクリックすると配線を接続できます。接続すると●(黒丸)になります。

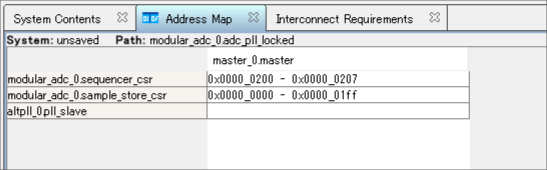

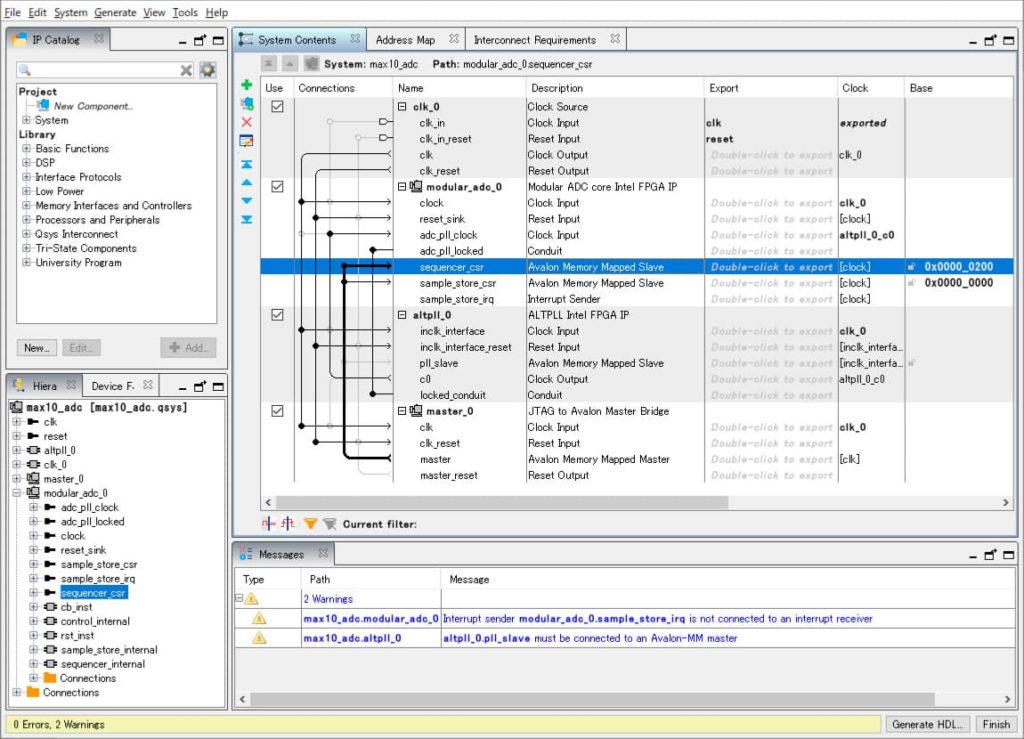

アドレス設定

Address Mapタブに移動してて、ADCモジュールのメモリマップアドレスを設定します。

- sequencer_csr: 0x0000_0200 – 0x0000_0207

- smple_store_csr: 0x0000_0000 – 0x0000_01ff

自動で割り当てることもできます。

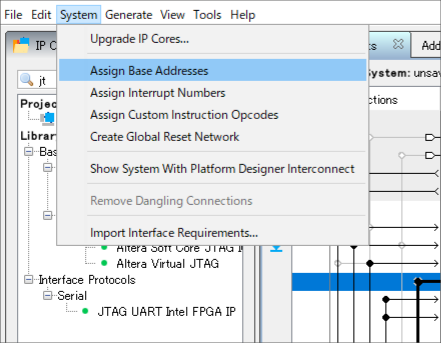

メニューの System → Assign Base Addresses をクリック。

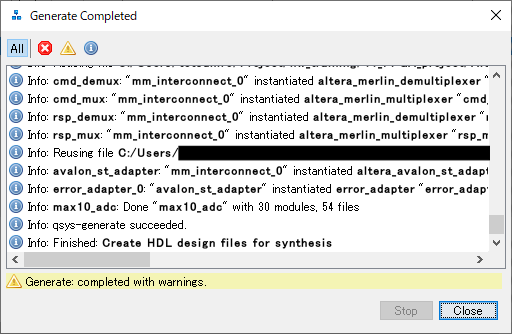

保存&HDL生成

エラーがないことを確認して、”Generate HDL”をクリック。(ワーニングはOK)

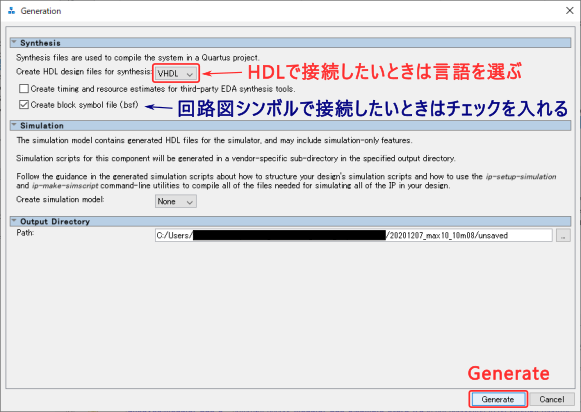

ここで作るモジュールとポートの接続にHDLを使いたい方は、生成する言語を選択。

回路図シンボルで接続したい方は、bsf生成のチェックボックスにチェックを入れておきます。

Platform Designerでの作業をファイルに保存するか聞かれる。Yesを選択して、保存先やファイル名を指定。

HDL生成が終わったら、進捗ウィンドウとPlatform Designerを閉じます。これでADCモジュールができあがり。

次は、生成したADCモジュールをトップモジュールに組み込んで、コンパイルです。

コメントを残す