自作USBブラスター用FPGAの続きです。

記事を4つに分けて書いていきます。

- ファイルの展開 ~ デバイス指定

- ピン制約(ピン定義)

- PLL設定・タイミング制約 ←現在地

- コンパイル・デバイスへの書き込み

目次

- 1. PLL 設定

- 2. ソースファイル追加

- 2-1. ソースファイルをプロジェクトに追加

- 2-2. トップソースを指定

- 2-3. ピン定義の補足

- 3. タイミング制約

- 3-1. Timing Analyzer 起動と Netlist Setup

- 3-2. クロックの制約を作成

- 3-3. SDCファイル書き出し

- 3-4. SDCファイルをプロジェクトに追加

PLL 設定

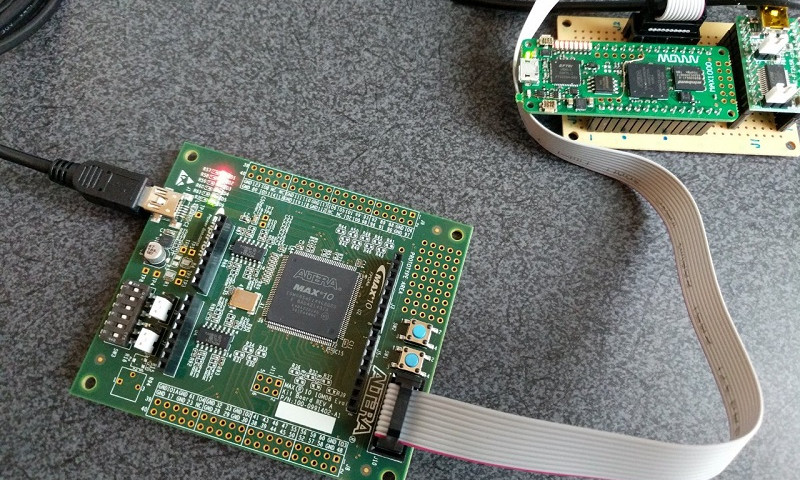

基板上のオシレータが 12 MHz に対して、今回のデザインで使用するクロックは 24 MHz です。

MAX10のPLLを使って、12 MHz のクロックから 24 MHz のクロックを生成して使用します。

IP選択

Quartus の右のほうにある IP Catalog の検索欄に「pll」と入力します。

pll で絞り込まれた候補のうち、ALTPLLをダブルクリックします。

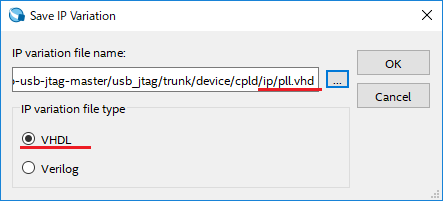

epm7064.qpf があるフォルダに、IP というフォルダを作ってその中に pll.vhd というファイル名を指定しました。 (このあたりは好みで構わないけど、ファイルパスに日本語とスペースを含まないようにしましょう)

file type は VHDL を選びましたが、Verilog な方はそちらをどうぞ。OK をクリックします。

PLL IP設定

変更する項目だけ挙げていきます。

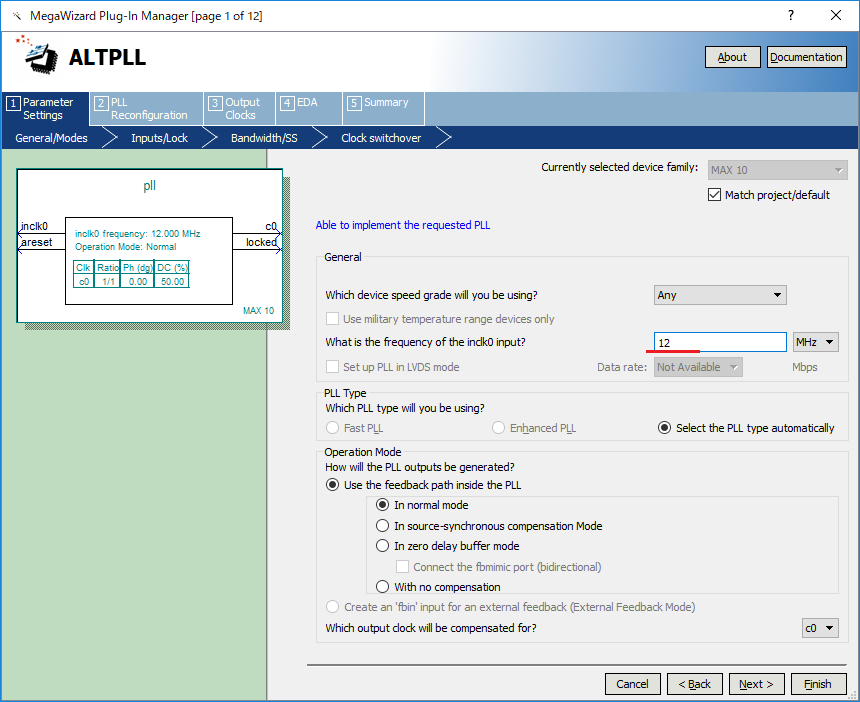

[1] Parameter Settings – General/ModesWhat is the frequency of the inclk0 input? に 12 MHz と入力

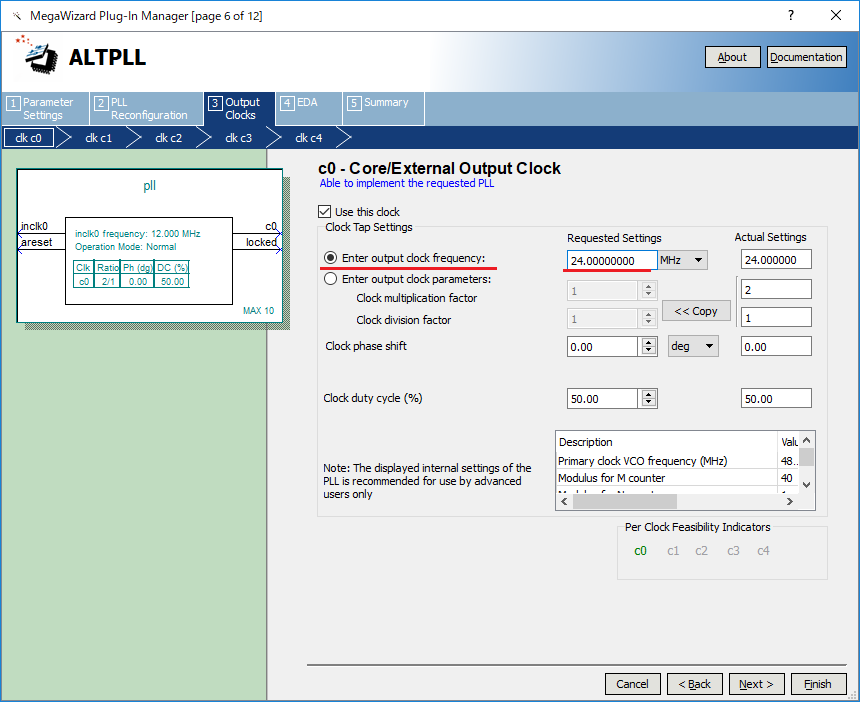

Enter output clock frequency を選択

Requested Settings で 24 MHz と入力

残りのページは変更なしです。右下の Finish をクリックして終了です。

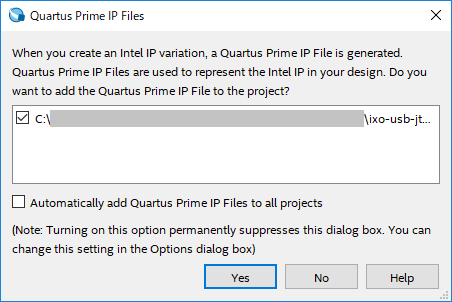

ファイルの追加確認ウィンドウが出た場合は、Yes をクリックしてプロジェクトへ追加しておいたらいいと思います。No を選んでも後で手動で追加するので、どちらでも大丈夫です。

ソースファイル追加

作成した PLL と、ダウンロードし使用している jtag_logic をつなぐためのソースファイルを作ります。

ソースはGitHubに置いてあります。(jtag_logic_top.vhd)

ソースファイルをプロジェクトに追加

上記のソースファイルをプロジェクトに追加します。VHDLのファイル名は jtag_logic_top.vhd です。

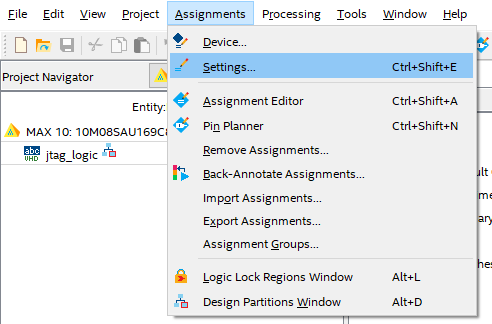

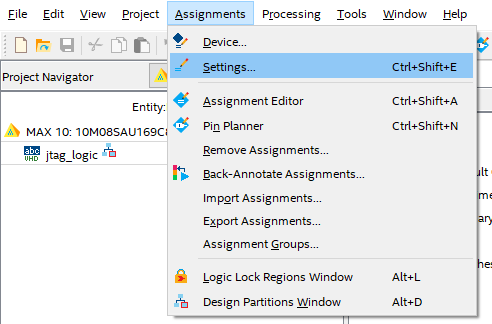

Quartus のメニュー、Assignments → Setting をクリックします。

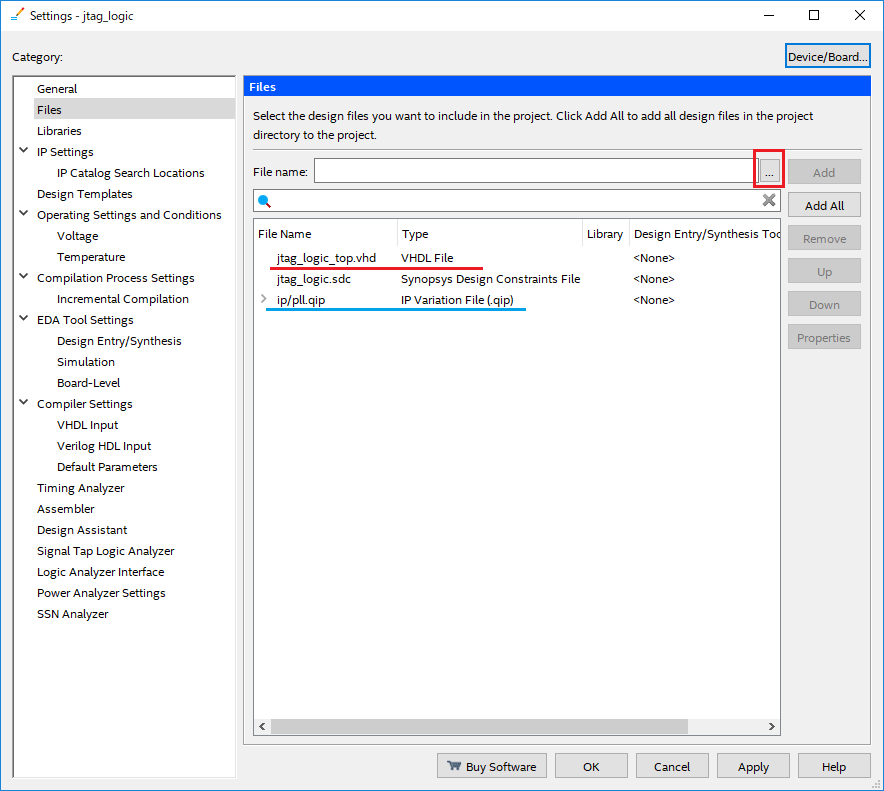

左側のメニューから Files を選びます。

File name の右のほうの「…」をクリックして、 jtag_logic_top.vhd を選びます。

下のファイル一覧に追加されればOK。

PLLを追加していない場合は、同様に pll.qip ファイルを選択して追加しましょう。

追加できたらOKをクリックして閉じます。

トップソースを指定

追加した jtag_logic_top.vhd をトップに指定します。

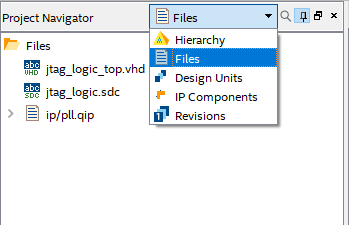

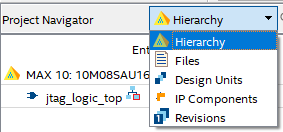

左上のほうの Project Navigator で Files に切り替えます。

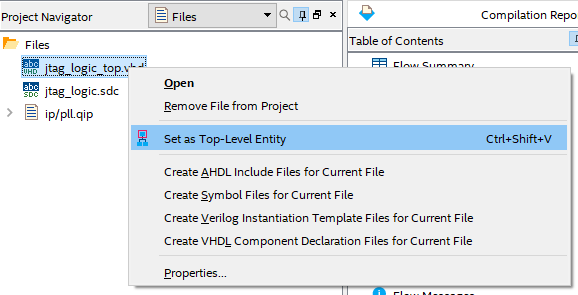

その中に先ほどの jtag_logic_top.vhd があるので、右クリックから Set as Top-Level Entity を選択。

Project Navigator で Hierarchy に切り替えると、図のように jtag_logic_top.vhd がトップになっています。

ピン定義の補足

正解はないですが、トップソースが決まってからピン制約をした方がいいと思います。

ポート名が変わったり、増減したら二度手間になるので・・・

タイミング制約

クロックの周期をタイミング制約に追加します。

コンパイルにおいて、ここで設定した周期を満たすように内部の配線長が調整されます。

Timing Analyzer 起動と Netlist Setup

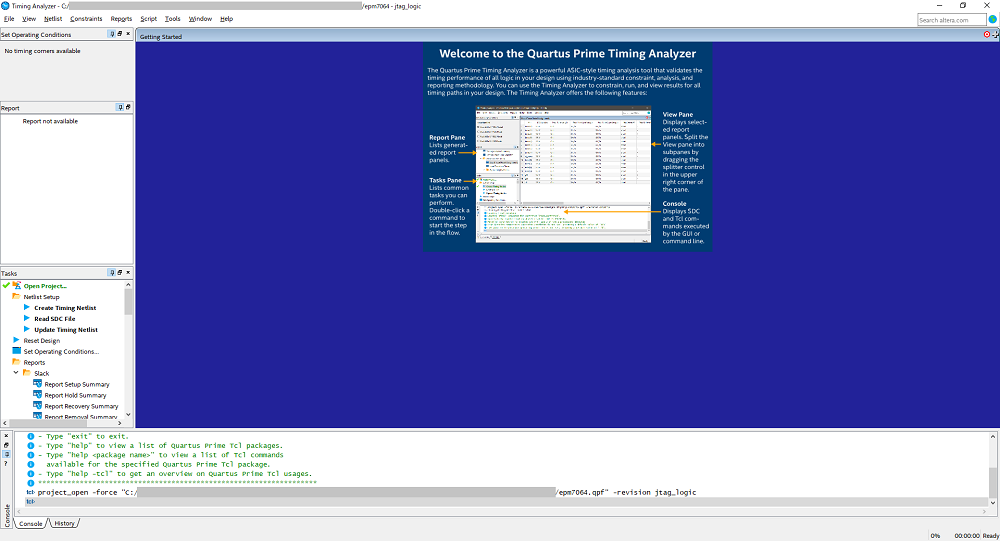

Timing Analyzer アイコンをクリックして Timing Analyzer を起動します。(以前のバージョンでは TimeQuest Timing Analyzer、名前変わってる。)

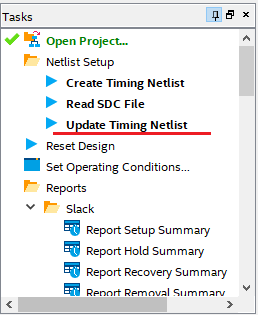

起動したら、Update Timing Netlist をダブルクリックしてネットリストをアップデートします。

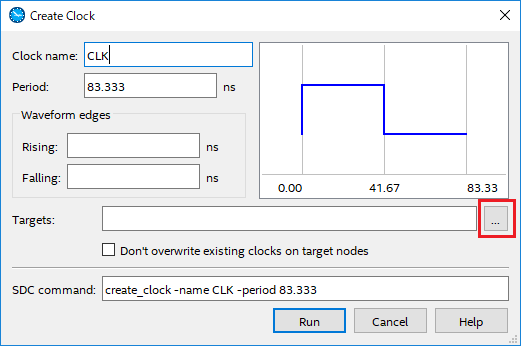

クロックの制約を作成

クロックの制約を追加します。

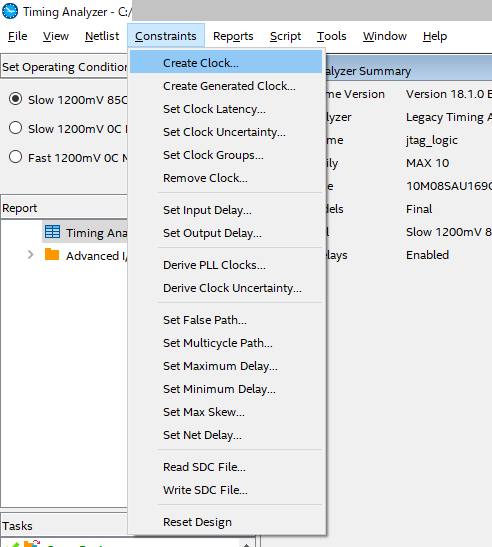

メニューの Constraints → Create Clock をクリックします。

MAX1000 の基板上にある 12 MHzのオシレータを使用するので、その情報を追加します。

12MHzの周期は、1/12(MHz) = 83.333(ns)

ソースのポート宣言でクロックのポート名は CLK なので同じ名前にしておきます。

- Clock name: CLK

- Period: 83.333

次に Targets の右の方の「…」ボタンをクリックします。

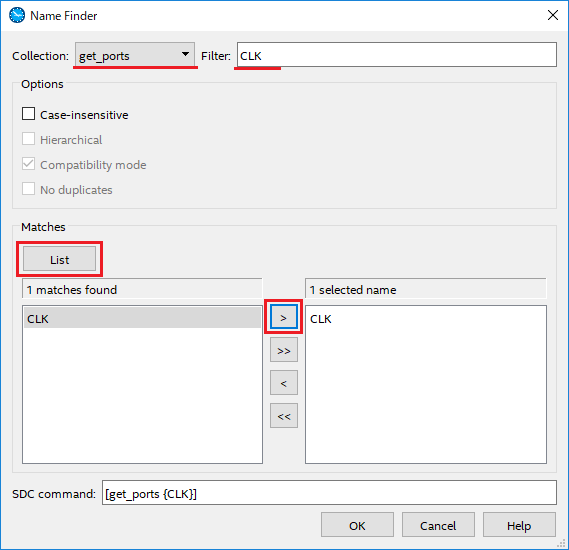

Name Finder ウインドウが出てきます。

Collection は、 get_ports を選択

Filter に、 CLK と入力

の状態で List ボタンをクリックします。

ボタンの下側に CLK が出てくるので 「>」ボタンをクリックして、CLK を右側に追加します。

その後、OK をクリックして閉じます。

Create Clock ウィンドウに戻ると、SDC Command に

が入力されているはずです。RUN をクリックします。

Timing Analyzer の画面に戻るとオレンジになれば正常です。

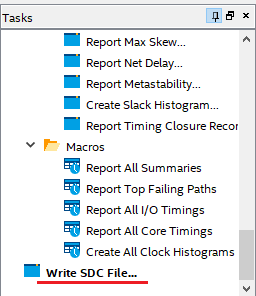

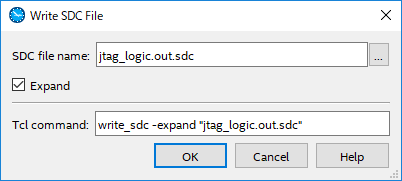

SDCファイル書き出し

Tasksの一番下の Write SDC File をダブルクリックします。

Write SDC File は内容を変更せずに OK をクリックします。

ファイルへの出力は以上です。Timing Analyzer は閉じましょう。

余談ですが、 jtag_logic.out.sdc ファイルをテキストエディタで開くと先ほどの内容が書かれています。

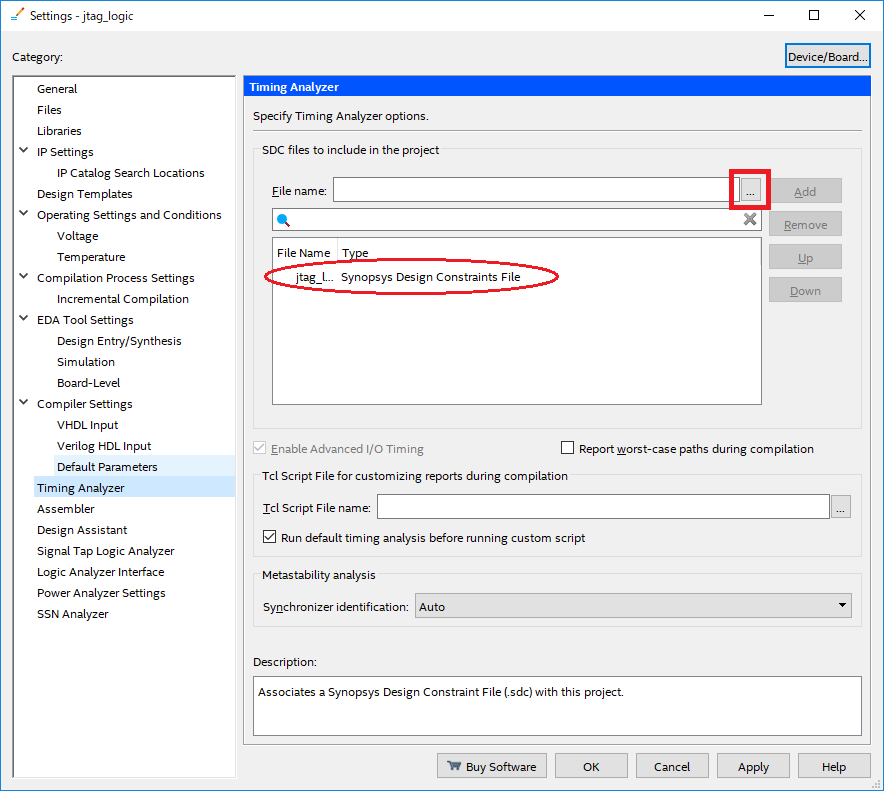

SDCファイルをプロジェクトに追加

作成したSDCファイルを、Quartus でプロジェクトに追加します。

その前に、ファイル名を jtag_logic.sdc に変更しましょう。

(間違えて Timing Analyzer から上書きしないために)

Quartus のメニューで、Assignments → Setting をクリックします。

Setting ウィンドウで、左側の Timing Analyzer をクリックします。

右の「…」をクリックして、先ほどのSDCファイルを選択します。

下側にファイルが追加されればOKです。

コメントを残す