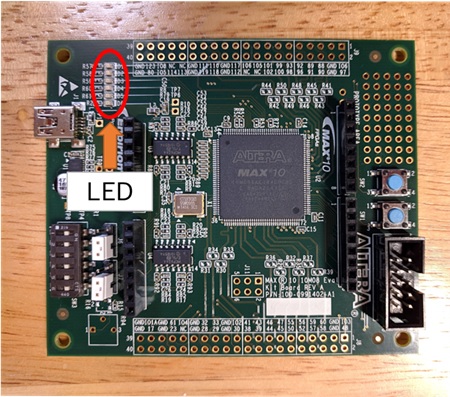

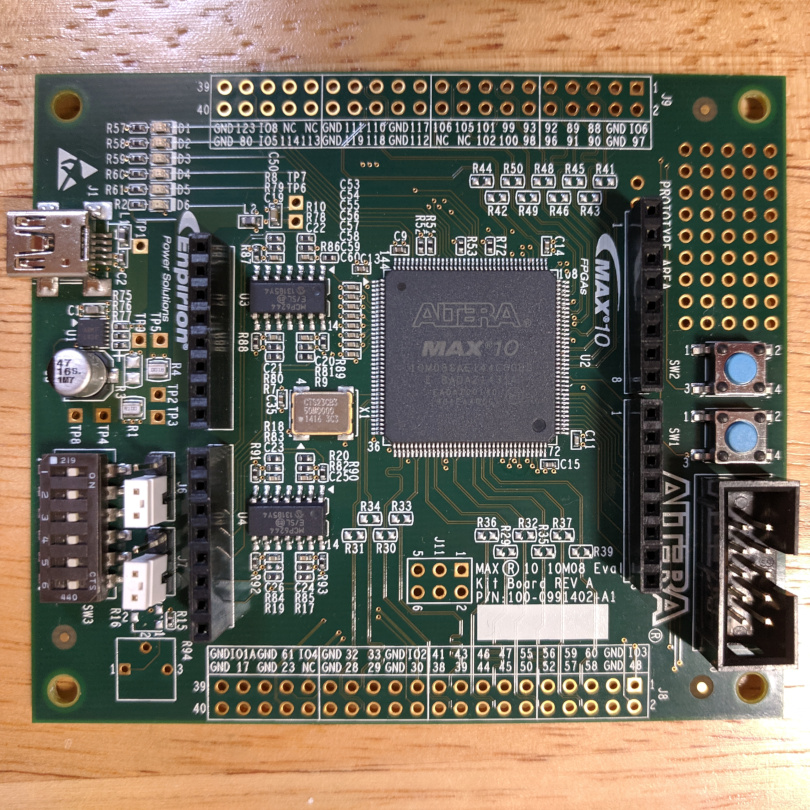

MAX10 Evaluation Kitを使って、MAX10にNios(CPU)を作ります。そしてCPUからソフト制御でLEDを点滅させてみます。LEDが5個あるので、まずはそのうち2個をハード制御します。

目次

- 1. ハード制御とソフト制御

- 2. 設計の流れ

- 3. ブロック図

- 4. Lチカ(HW制御)とQuartus Primeプロジェクト

- 4-1. VHDLソース

- 4-2. プロジェクト作成 (New Project Wizard)

- 4-3. ソースファイルを追加

- 4-4. PLLのIPコア作成

- 4-5. モジュール構成の認識 (Analysis & Elaboration)

- 4-6. ピン配置 (Pin Planner)

- 4-7. タイミング制約

- 4-8. プロジェクト内のファイル(確認)

- 4-9. コンパイル

- 4-10. デバイスへ書き込み

- 5. 動作確認

ちなみに私のソフトのスキルはPC上でpythonをちょくちょくいじれる程度で、初ファームウェア設計です。。

冒頭に書いた通り、このボードにはユーザが制御できるLEDが5個あるので2個はハード制御、残り3個はソフト制御にします。

ハード制御とソフト制御

- ハード制御 (ハードウェア制御)

ハード側から制御する場合は、HDL(VHDLやVerilig-HDL)で動作を記述します。

大まかにいうと、HDLのソースコードを元にツールが回路を合成します。 - ソフト制御 (ソフトウェア制御)

ソフトウェア制御では、FPGA上に作ったCPUに命令を実行させるようにC言語などでファームウェアを設計します。

設計の流れ

- 全体の仕様検討

- ハードウェア設計 (LED制御回路)

- ハードウェア設計 (CPU)

- ソフトウェア設計、コーディング、デバッグ

の流れで進めていきます。

全体設計 → CPU設計 → ソフト設計 の順番が入れ替わってなければ大丈夫かと。ハードウェアのLED制御回路設計はCPU&ソフトとは完全に独立して進められるので。

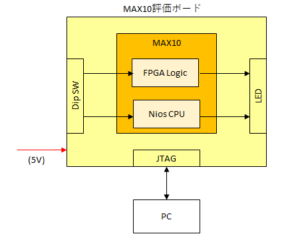

ブロック図

ブロック図はこんな感じです。

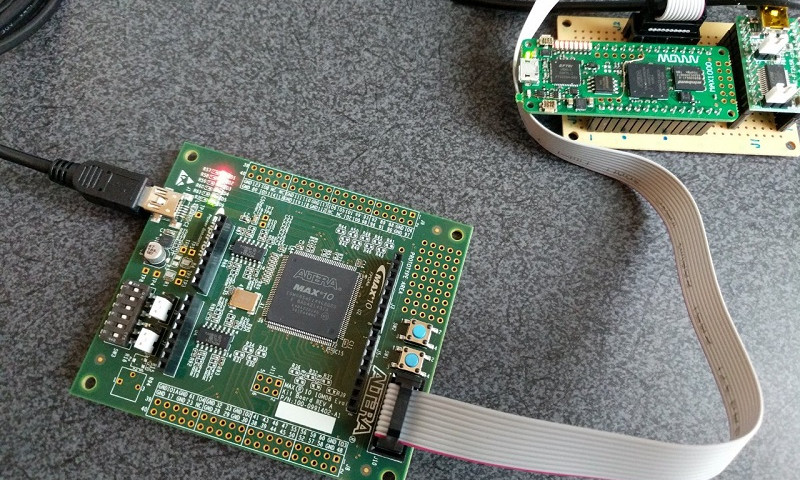

(最終的には)スイッチで点滅速度を変えられるようにしようと思っているぐらいで、基本的には電源を入れるとLEDが点滅し続けるだけを考えています。なので、FPGA(とCPU)と外部のやりとりは、基板上のスイッチとLEDだけになります。

電源は基板外から供給する必要があるので、電源ケーブル(USBケーブル)だけが外につながる予定です。設計途中では、JTAGコネクタに電源の他にUSBブラスターをつないでプログラムの書き込みなどを行います。

Lチカ(HW制御)とQuartus Primeプロジェクト

VHDLソース

省略。完成品はこちら。。(準備中)

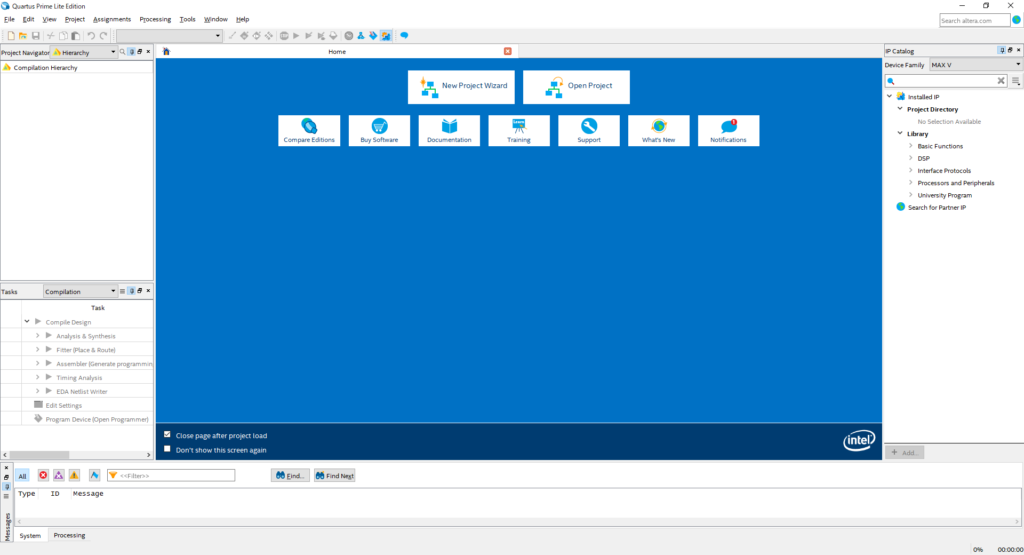

プロジェクト作成 (New Project Wizard)

開発環境にプロジェクトを作成します。まず、Quartus Primeを起動。

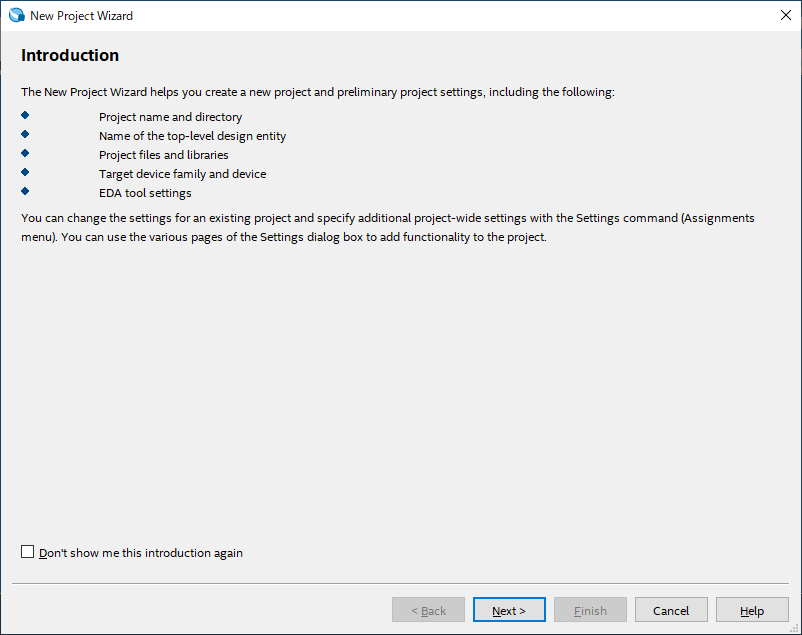

New Project Wizardをクリックしてプロジェクトを作っていきます。

プロジェクト名を適当に決めて、Nextをクリックして進んでいきます。

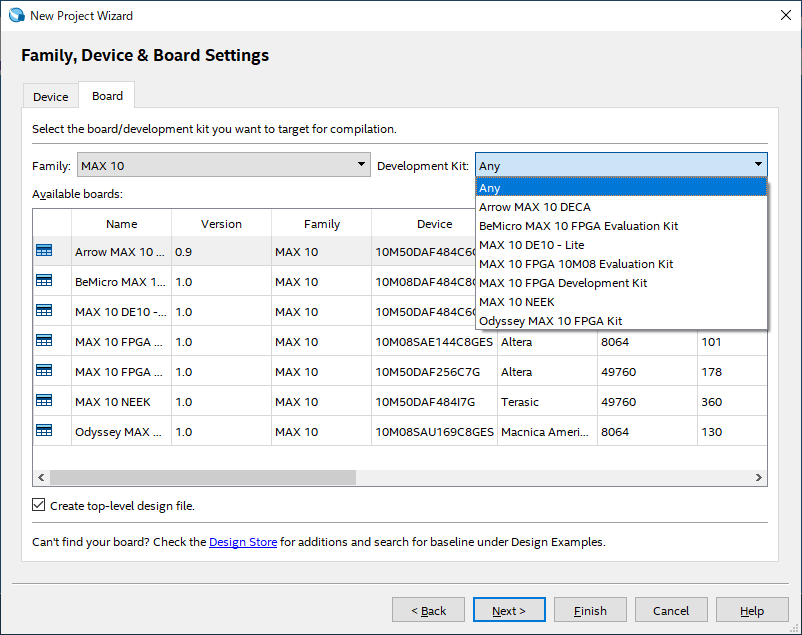

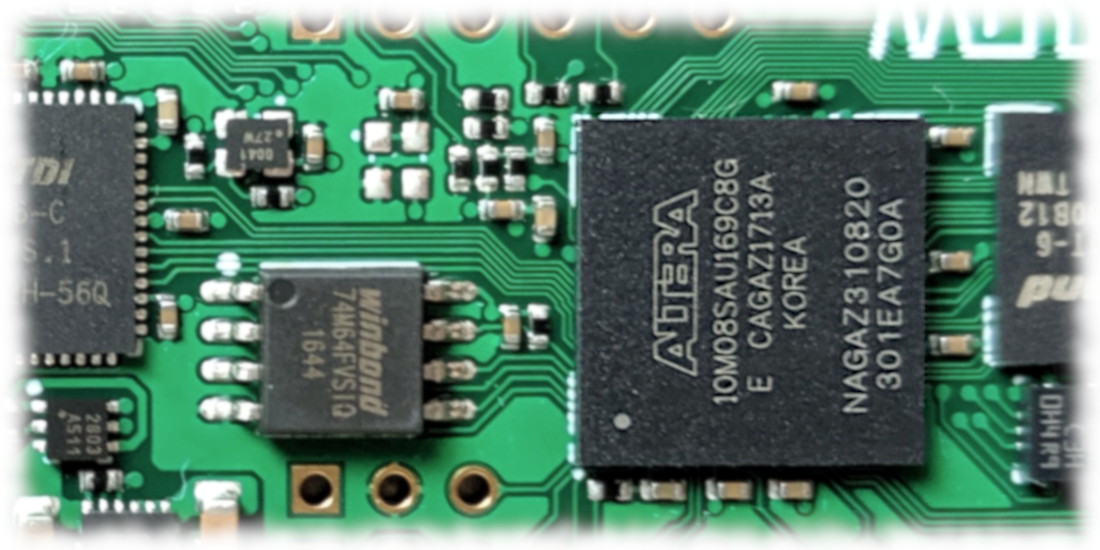

下の図はデバイス選択の画面です。FPGAデバイスの型番を選択してもいいんですが、隣の[Board]タブの中に使用する評価ボードが用意されていればそれを選択するとお手軽です。今回はMAX10 FPGA 10M08 Evaluation Kitが選択肢にあったのでこちらから選択しました。

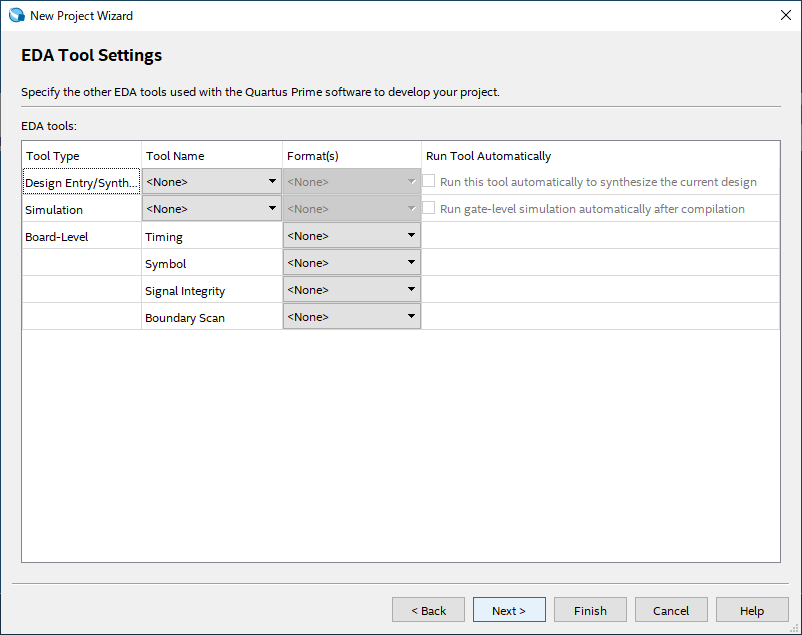

EDA Tool Settingsは今回はデフォルトのままいきます。

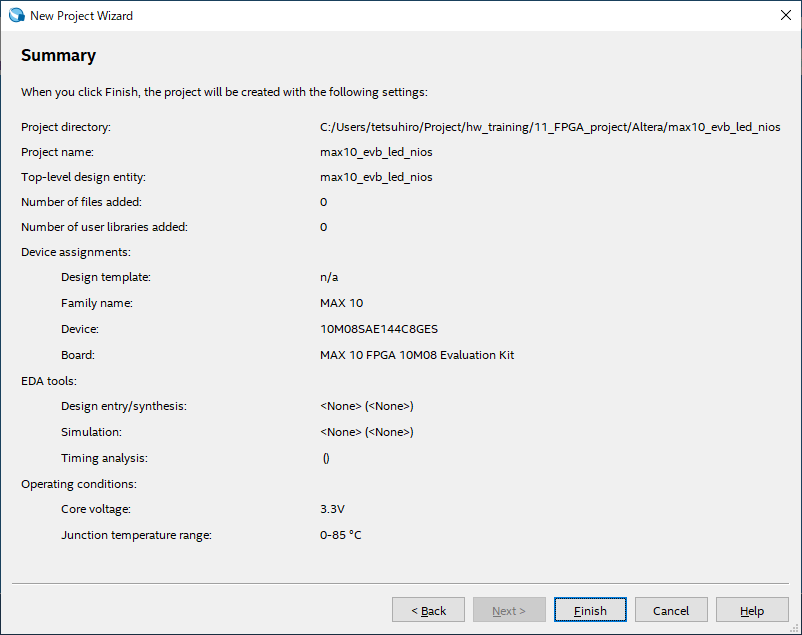

サマリです。

- Family Name

- Device

- Core voltage

- Junction temperature range

も自動で設定されています。

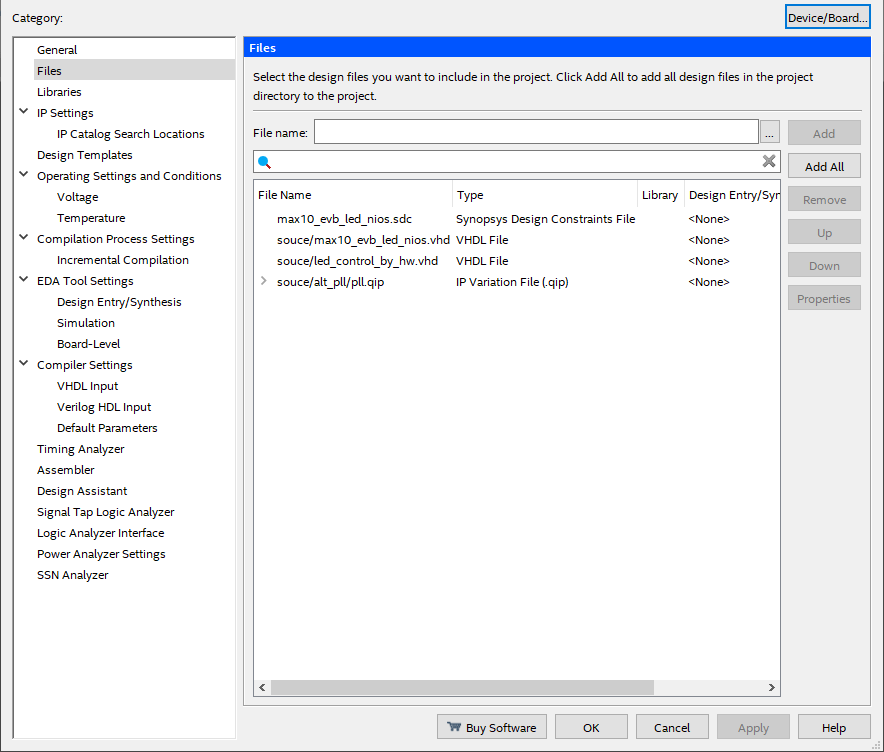

ソースファイルを追加

Quartusのメニューバーから Settingsウィンドウ を開きます。(以下のどちらか)

- Project → Add/Remove Files in Project

- Assignments → Settings

Categoryで File を選びます。

そして、右側の File name 入力欄の右のほうにある […] をクリックして追加するファイルを選びます。トップのソースとLEDを点滅させるソースの合計2つを追加しました。

PLLのIPコア作成

省略。こちらの記事が参考になります。。

MAX10 FPGA (3: PLL設定・タイミング制約) 【自作USBブラスター】 | てつふくブログ

自作USBブラスター用FPGAの続きです。 記事を4つに分けて書いていきます。 ファイルの展開 ~ デバイス指定ピン制約(ピン定義)PLL設定・タイミング制約 ←現在地コンパイル・デバイスへの書き込み 目次 1. PLL 設定 1-1. IP選択 1-2. PLL IP設定 2. ソースファイル追加 2-1.

モジュール構成の認識 (Analysis & Elaboration)

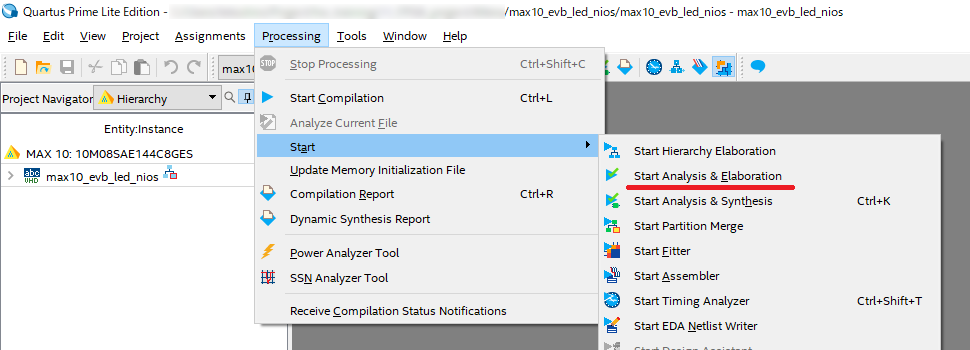

ピン配置などを設定しますが、まず開発ツール側にソースファイルの構成を認識させる必要があります。

普通にフルコンパイルするか、Processing → Start → Analysis & Elaborationを実行します。(コンパイルに数時間かかるような大きなFPGAのときはフルコンパイルはやめておいた方がいいかも)

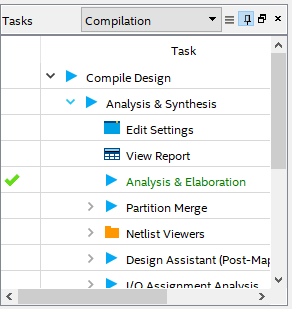

Analysis & Elaboration の場合は、完了すると Tasks の Analysis& Synthesis の下にあるAnalysis & Elaboration にチェックが入ります。

ピン配置 (Pin Planner)

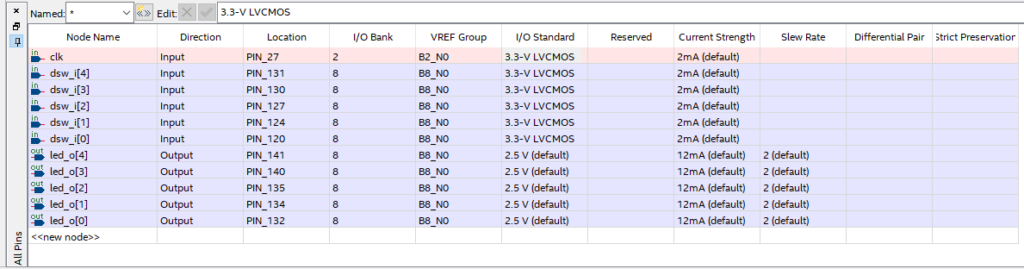

トップソースで定義したポートを、デバイスのピンに割り当てます。

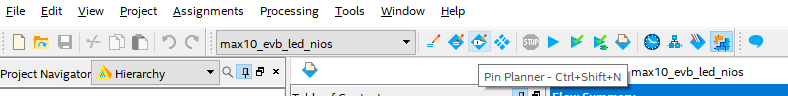

Pin Planner を起動します。

次のように設定しました。

設定が完了したらPin Plannerは終了しておきます。

タイミング制約

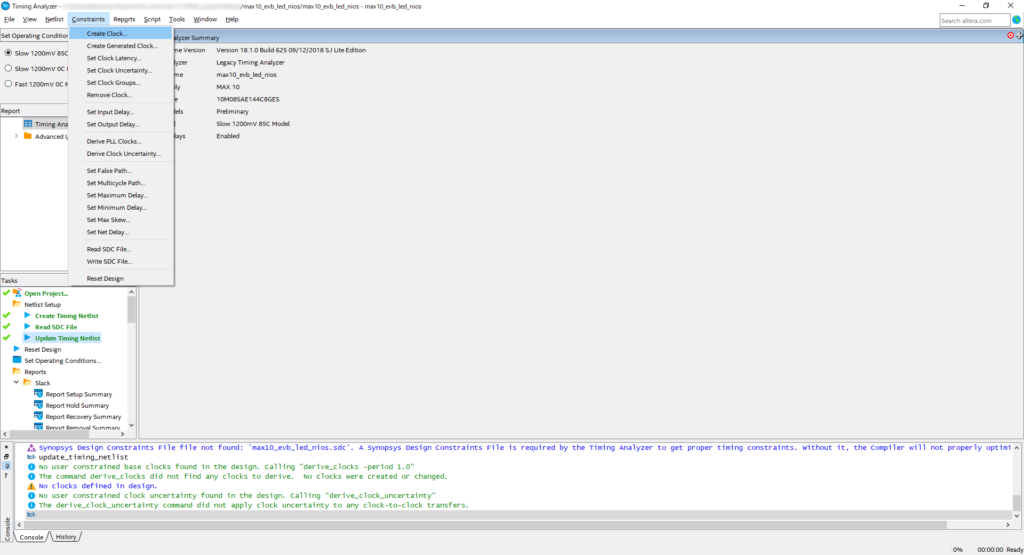

Timing Analyzer

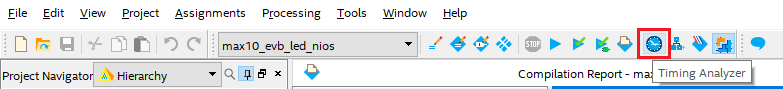

Tool → Timing Analyzer か、アイコンからTiming Analyzerを起動します。

起動したら、Tasksの

- Create Timing Netlist

- Read SDC File

- Update Timing Netlist

を順にダブルクリックして実行します。

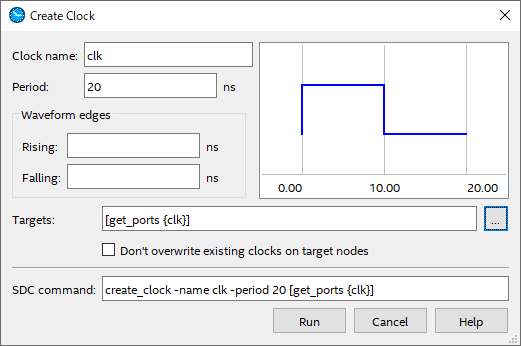

Constraints → Create Clock の順にクリックして、Create Clockウィンドウを開きます。

Create Clockウィンドウでは次の内容を入力してRunをクリックします。

Timing Analyzer Summaryの背景がオレンジ色になればOKです。

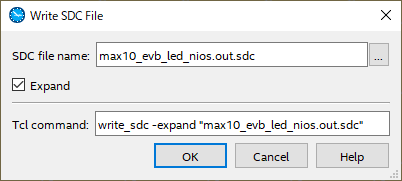

Tasksの一番下の Write SDC File をダブルクリックしてSDCファイルを出力します。

ファイル名が ~.out.sdc になっていますが、最終的には ~.sdc にします。

ここで出力ファイル名を変更してもいいし、Windowsのエクスプローラでファイル名を変えてもいいです。

ファイル出力ができたら Timing Analyzer を終了します。

SDCファイルに追記

出力されたSDCファイルにPLLで生成するクロックに関する記述を追記します。SDCファイルをテキストエディタで開きます。

create_clockの行は先ほど追加した内容です。それより下ならどこでもいいので、derive_pll_clocksと書かれた行を追加します。追加したら上書き保存します。

derive_pll_clocksはPLLなどで自動生成したクロックへの制約を自動的に行ってくれるコマンドです。Timing AnalyzerのGUIからは設定できないので、テキストエディタで直接記述します。ちなみに、このderive_pll_clocksはSDCの標準コマンドではなくアルテラの拡張コマンドです。

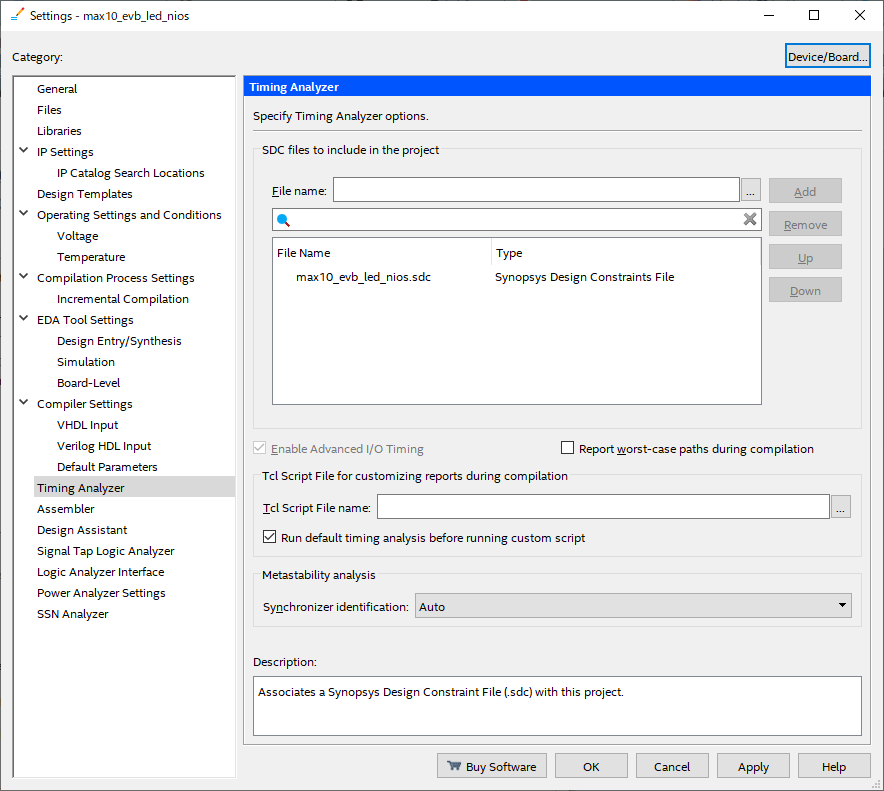

SDCファイルをプロジェクトに追加

SDCファイルをQuartusのプロジェクトに追加します。

Assignments → Settings で Settings ウィンドウを開いて、Categoryで Timing Analyzer を選択します。

File name 入力欄の右のほうにある […] をクリックして、先ほどのSDCファイルを追加します。

ファイルを追加したら、OKをクリックしてウィンドウを閉じます。

プロジェクト内のファイル(確認)

PLLも別途追加しているので、ファイルリストは↓のようになっています。参考まで。

コンパイル

Quartusでコンパイルします。開始方法はいろいろあるのでお好きな方法でどうぞ。

- TasksのCompile Designをダブルクリック

- ツールバーの▶アイコン

- Processing → Compilation

- ショートカットキー(Ctrl + L)

Tasksの Compile Design が緑色になってにチェックがつけば完了。

レポート確認

右のほうのコンパイルレポートで、Timing Analyzerのところが赤色になっていると思います。

Timing Analyzer → Unconstraints Path と展開して、Unconstraints Clocks が0なら大丈夫です。(出力信号にも制約をかけると赤文字はなくなるんですが、とりあえず今は大丈夫ということで)

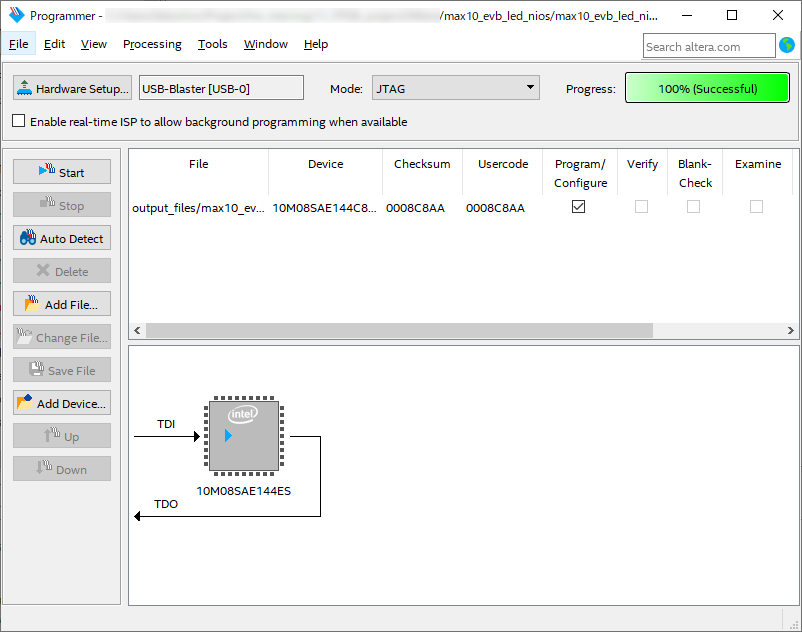

デバイスへ書き込み

コンパイルが問題なく終われば、デバイスへ書き込むためのファイルがoutputフォルダに出力されています。~.sofと~.pofです。

sofファイルとpofファイル

どちらを書き込んでも動作するんですが、

- sofは電源オフで内容が消えます。

デバッグやちょっとした確認したいときは、電源を落とすと書き込み内容がクリアされるので元のプログラムを汚さずに作業できます。 - pofを書き込むと電源オフでも内容が消えません。

次回電源投入時に自動的に書き込んだプログラムが動作します。sofより書き込み時間が長い。

Programmerの起動

以下の方法で、Programmerを起動します。

- Tasksの一番下

- ツールバーのアイコン

- Tool → Programmer

USBブラスター的なものを使って、sofファイルを書き込みました。

動作確認

細かいことまで見てませんが、ちゃんと動いてます。

VHDLで、MAX10でLチカさせてみた。https://t.co/edIJQPQ1PU pic.twitter.com/2njvvzeSxw

— てつふく (@tetsufuku81) August 31, 2019

コメントを残す