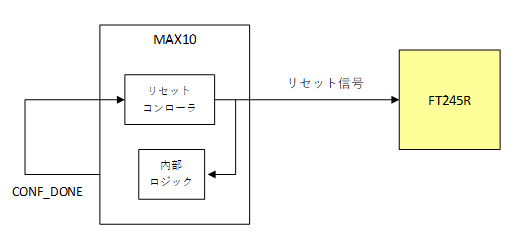

リセット系統の検討。

FPGAがリセット信号を出力して、FPGA自身とFT245RLモジュールにリセットをかけます。

リセットのトリガは、MAX1000のリセットボタン(プッシュスイッチ)と、パワーオンリセット(Power on Reset)にします。

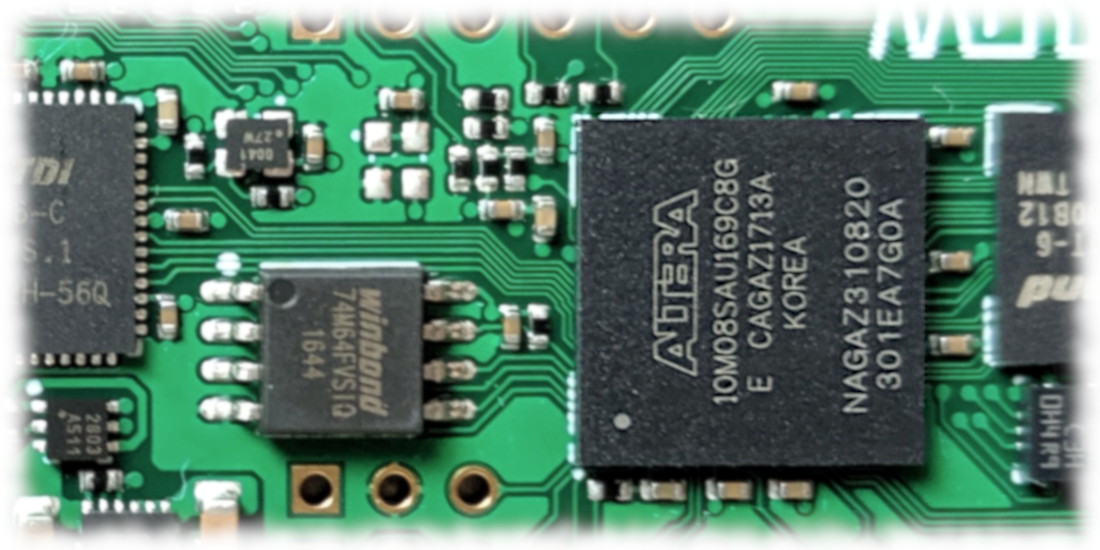

・・・という予定でしたが、リセットボタンの接続先を確認すると、ユーザIOではなくコンフィグ用のnCONFIGピンでした。

設定すればユーザIOとしても使えますが、推奨されてはいないのでユーザのリセット制御に使うのはやめておきます。

目次

- 1. リセット系統図

- 2. FPGAリセット回路

- 2-1. 初期リセット

- 2-2. リセットボタンからのリセット

- 2-3. HDL設計

リセット系統図

CONF_DONE信号を監視

↓

リセットコントローラで64 ms後にリセット解除

↓

FPGA内部とFT245Rが動作開始

FPGAリセット回路

初期リセット

本音を言えば電圧監視をしたいんですが、MAX10のADCが使えるかどうかわかってない現状です。

とりあえずコンフィグ完了からの時間でリセット解除する方向で設計します。根拠はないけど64 ms。

コンフィグ完了はどの信号を見てたらいいのかなぁ。CONF_DONEですね。

CONF_DONEがリリースされた64 ms後に、システムのリセットを解除します。

リセットボタンからのリセット

先走っていろいろ考えてたんですが、回路図をよく見るとコンフィグピンであるnCONFIGに直結してました。なので、ボタンを押すと無条件にリコンフィグになります。

初めは↓の予定でしたが・・・。

プッシュスイッチからの入力信号を監視しておきます。

MAX10のIO Standardにシュミットトリガがあるので、使ってみます。

チャタリング除去が必要なのかはユーザガイドだけでは判断しきれないので、自前の除去回路を入れておきます。

(オシロで波形確認したいところ…)

HDL設計

つづく

リセットコントローラのHDL設計 【自作USBブラスター】 | てつふくブログ

今回作る「USBブラスター的なもの」のリセットコントローラの動作の概要です。

コメントを残す