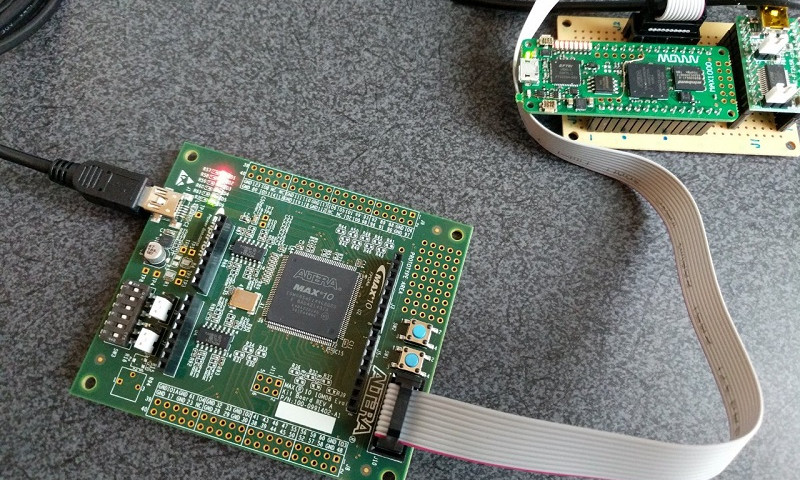

MAX10評価ボードのMAX1000を使うことにして回路図を見ていたら、ボード上にFT2232Hが載っていました。

外部にICを追加せずに、基板上のものを使えないか検討してみました。

目次

- 1. 配線数不足で使えず

- 2. 変換ICとFPGAの接続

-

- 2-1. ブロック図

- 2-2. JTAGへの接続

- 2-3. GPIO (汎用的な接続

- 3. 変換ICは外部配置に決定

-

- 3-1. 外部コネクタとMAX10の配線を確認

-

- 3-1-1. (余談) 外部IOにつながる抵抗

- 3-2. 外部IOの電圧を確認

- 4. まとめ

-

- 4-1. 基板上の変換ICは使えない

- 4-2. USB変換ICは外部に配置

配線数不足で使えず

結論としては、今回は使えません。

FPGAとの変換ICをつなぐバス幅が足りないからです。

変換ICとFPGAの接続

ブロック図

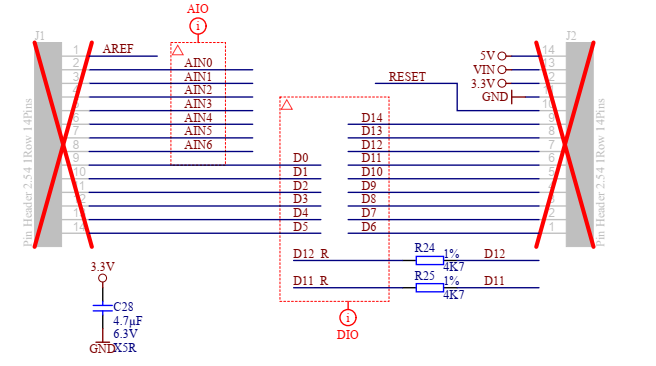

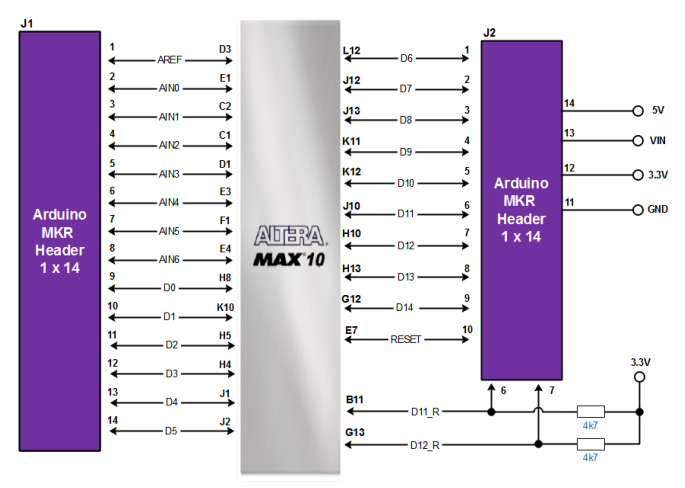

USB変換IC(FT2232H)とFPGA間は下図のようになっています。

変換ICのFT232H(黄色で示す)には2系統のIOがあります。

- JTAG (JTAGコネクタおよびFPGAのBank 10へ接続)

- 汎用的なGPIO (FPGAのBank 8へ接続)

JTAGへの接続

FT2232Hから直接MAX10のJTAGピンに接続されています。

Arrowの専用ドライバを使うとJTAGチェーン上のデバイスが見るようになります。

そのほかに、MAX10に向かう途中で分岐して基板上のVIAにもつながっています。

JTAG信号を外部に引き出すことができるので、ここからJTAGチェーンを組めないか考えてみました。ですが、このVIAからJTAG信号を外部に出してもMAX10を含むデイジーチェーンにはなりません。

パラレル接続しようにも、TMSがT分岐しているので、(基板改造しなければ)無理そうです。

GPIO (汎用的な接続)

次に、FT2232Hのもう1つのチャンネル(ポート)からMAX10を経由して構成できないか検討しました。

使う予定のFPGAデザインでは、変換ICとFPGAの間に12本の配線が必要です。ですが、さっきのブロック図のとおり6本(6bit)の配線しかありません。

使用予定のデザインはこちらにダウンロード先を書いています↓

変換ICは外部配置に決定

以上の理由でMAX1000基板上のUSB変換ICを使い回すことはできませんでした。そのため、外部にUSB変換ブロックを設ける必要があります。

MAX1000の外部コネクタとFPGA間の配線に問題がないか確認しておきます。(ピン数と電圧を確認します。)

外部コネクタとMAX10の配線を確認

回路図で確認します。

両端の☓印は未実装のコネクタです。電源やGND以外の配線を確認します。

AIN0~6の7本とD0~14の15本、合計22本がMAX10につながっています。必要な本数は前述のとおり12本なので問題ありません。

また、FPGAから出力する新しいJTAG信号も同じコネクタを経由して基板外に出しますが、10本余っているので問題なしです。

(余談) 外部IOにつながる抵抗

上記の回路図にそれぞれ4.7kΩのR24とR25があって、信号線につながっています。この抵抗が何者かの確認です。

普通に考えると、この場所にこの抵抗値ならプルアップ抵抗のはずなんですよ。

ユーザーガイドにはこんな図(↓)もあるし。

回路図でも信号線の反対側がどこにつながっているかを確認しました。次のようになっています。

- D12_RはMAX10のBank 5

- D11_RはMAX10のBank 6

つまり、[MAX10] - [抵抗] - [コネクタ] 。

ということは、ダンピング抵抗?4.7kΩのダンピング抵抗?

回路図の誤記だと思います。以上、余談でした。

外部IOの電圧を確認

最後に外部IOの電圧を念のため確認しておきます。

- まず、信号がMAX10のどのバンクに接続されているかを確認

- 次に、そのバンクのIO電源電圧を確認

すべて3.3Vでした。特に問題なしです。

まとめ

基板上の変換ICは使えない

- JTAGをデイジーチェーン接続できない

- JTAGをパラレル接続するためのTMSが独立していない

- 別系統はMAX10との配線数が不足

USB変換ICは外部に配置

- コネクタとMAX10の間の配線数OK (12本必要なところ、22本ある)

- IO電圧は3.3Vで問題なし

コメントを残す