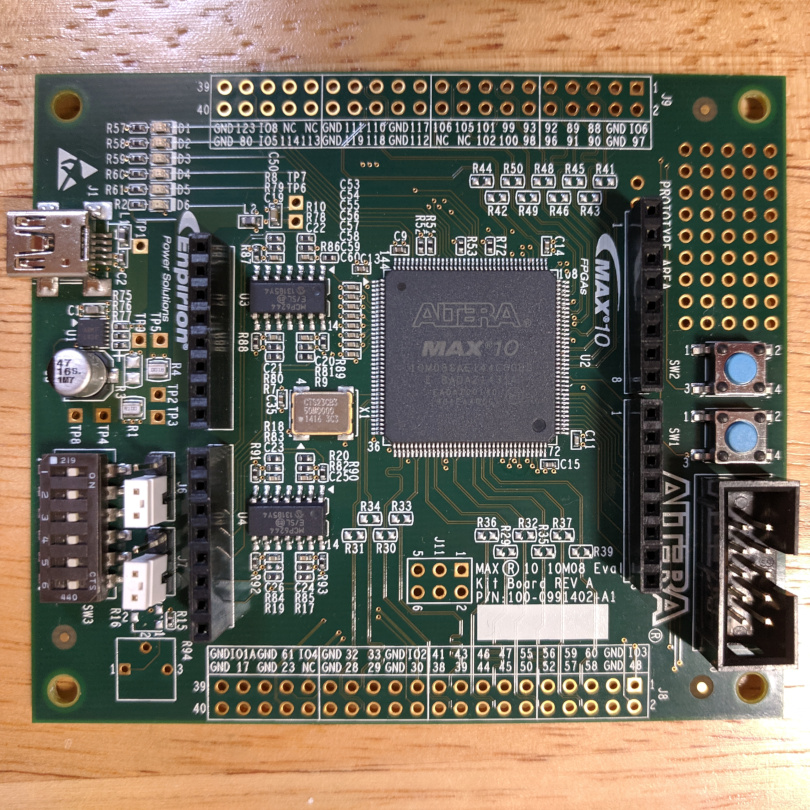

MAX1000とFT245RLモジュールの接続方法を考えます。

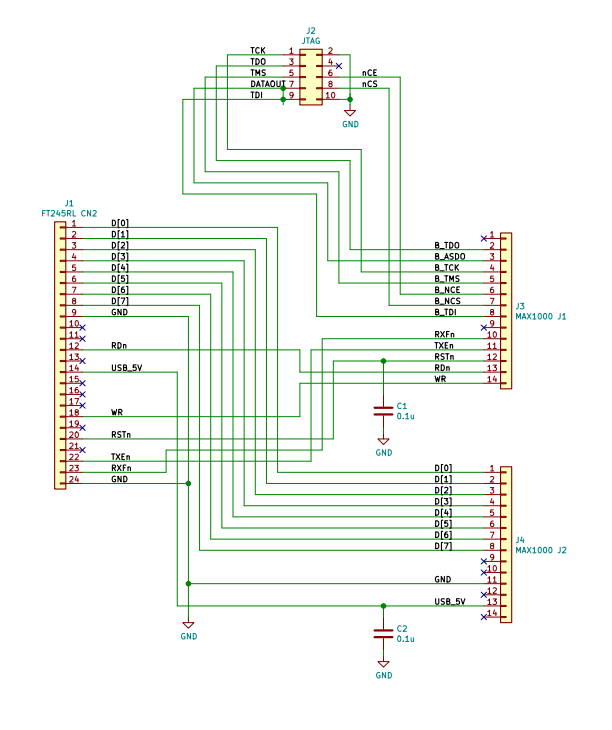

基板間接続回路図

JTAGコネクタも含めた回路図です。KiCADで描いています。

信号ライン

どちらも3.3 VのIOなので、デジタルの信号線はある程度適当でも大丈夫と思います。 気にしておきたいのが、電源とグランド(GND)とリセットです。

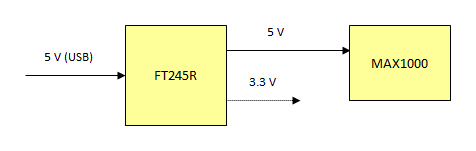

電源

電源はUSBケーブル経由でPCから供給します。

PCに接続する基板はPCと通信するFT245RLモジュールのほうなので、こちらに5Vが入ります。

MAX1000の電源はFT245RLモジュールから基板間で供給します。

- FT245RLモジュールから外部に出ている電源は5 Vと3.3 V

- MAX1000が外部から受けられる電源はVINの5 V

ということで、基板間は5Vで給電します。

FT245RとMAX1000の間の電源-GND間に 0.1uFのパスコンを1つ追加しておきます。

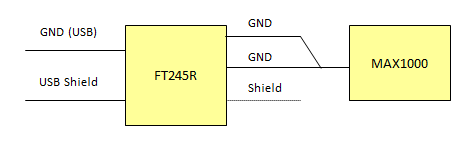

グランド (GND)

外部ピンに出ているGNDは、

- FT245RLモジュールから → FGを含めて3本 (GNDピン×2、USBシールド×1)

- MAX1000 → 1本

USBシールドはFGと考えて、ほかの合計3本を接続します。

リセット

- FT245RLモジュールにはリセット入力ピンがあります

- MAX1000にはリセットボタンがあります(ま、ただのプッシュスイッチです)

リセット系統

FT245RLモジュールは、リセットピンを未接続のままにしておくと内蔵のリセット回路が動作するようですが、今回はFPGAでリセットを制御するようにします。

MAX1000の方が起動に時間がかかりそうだからです。

初期リセットのほか、リセットボタンでもシステム全体にリセットがかかるようにします。

ということで、後ほどFPGAのリセット回路を設計して、リセット信号がMAX1000 → FT245RLモジュールと流れるようにします。

ノイズ対策に0.1uFのコンデンサを1つ入れておきます。

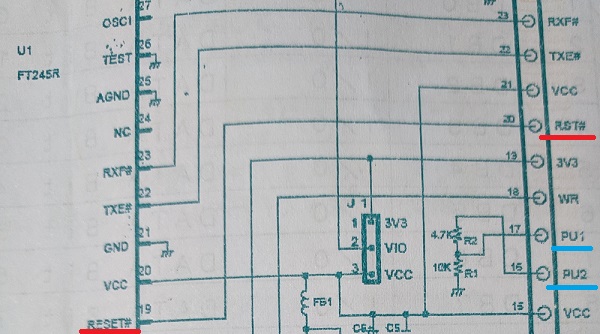

FT245RLモジュール内のリセット信号接続

モジュールの説明書には、外部リセットの際はPU1とPU2を使ってどうのこうのと書いてますが、これらのピンは5V入力時に分圧して3.4Vを生成するための抵抗分圧回路です。

今回はFPGAから3.3Vのリセット信号を出力するので、直接RESEST#ピンへ接続します。

これを見ながらユニバーサル基板に回路を作っていきます。

ユニバーサル基板にはピンソケットを実装して、それぞれのモジュールを取り外せるようにする予定です。

今後の予定

- ユニバーサル基板回路作成

- FPGAリセット回路設計

- ピン制約修正

コメントを残す