目次

トップモジュール作製・コンパイル

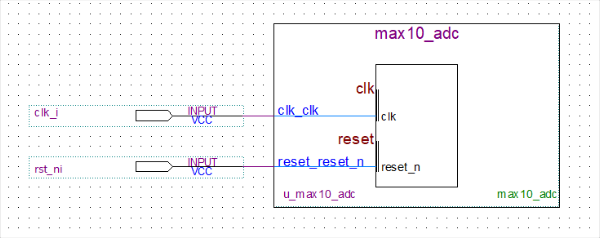

生成したモジュールとポートを接続。

回路図でもHDLでも、使いやすいほうでOK。

回路図で接続

HDLで接続 (これはVHDL)

モジュール名やポート名は、ご自分の環境に合わせて修正してください。

デザインファイルを追加

作成した回路図ファイルやHDLファイルと、Platform Designerで生成されたqipファイルがプロジェクトに追加できていることを確認。

回路図・HDLをトップに指定。

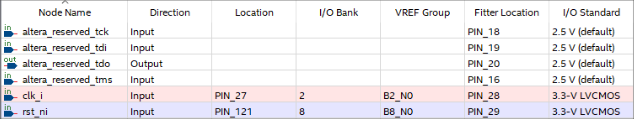

コンパイルと制約 (IO制約・タイミング制約)

コンパイルしましょう。制約も忘れずに。

ロケーションとIO Standardを次のように設定。(ご使用の環境に合わせてください!)

- clk_i : PIN_27, 3.3-V LVCMOS

- rst_ni : PIN_121, 3.3-V LVCMOS

タイミング制約はsdcファイルにクロック定義を1行。

create_clock -name {clk} -period 20.000 -waveform { 0.000 10.000 } [get_ports {clk_i}]ダウンロード

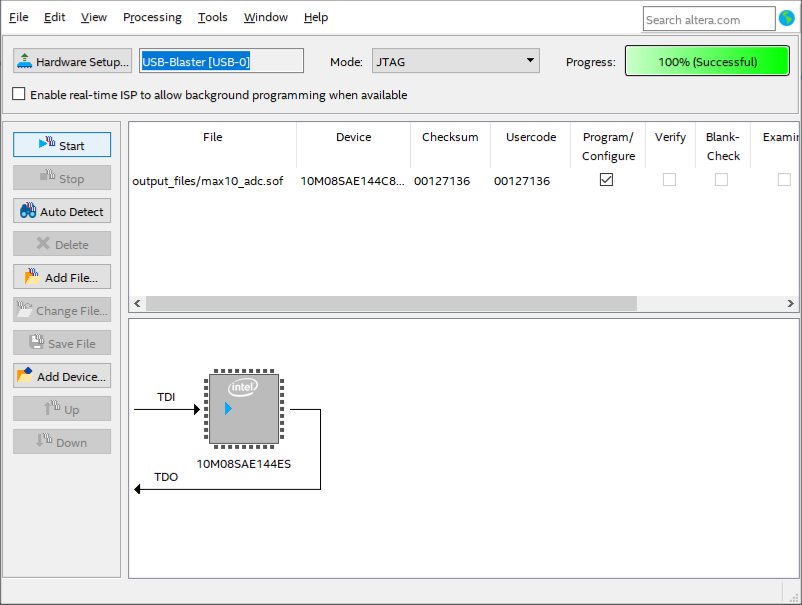

コンパイルが完了したら、QuartusのProgrammerを起動してsofファイルを書き込みます。

次は動作確認。ADCでTSDの値を読み出してみましょう。

コメントを残す