目次

はじめに

目的

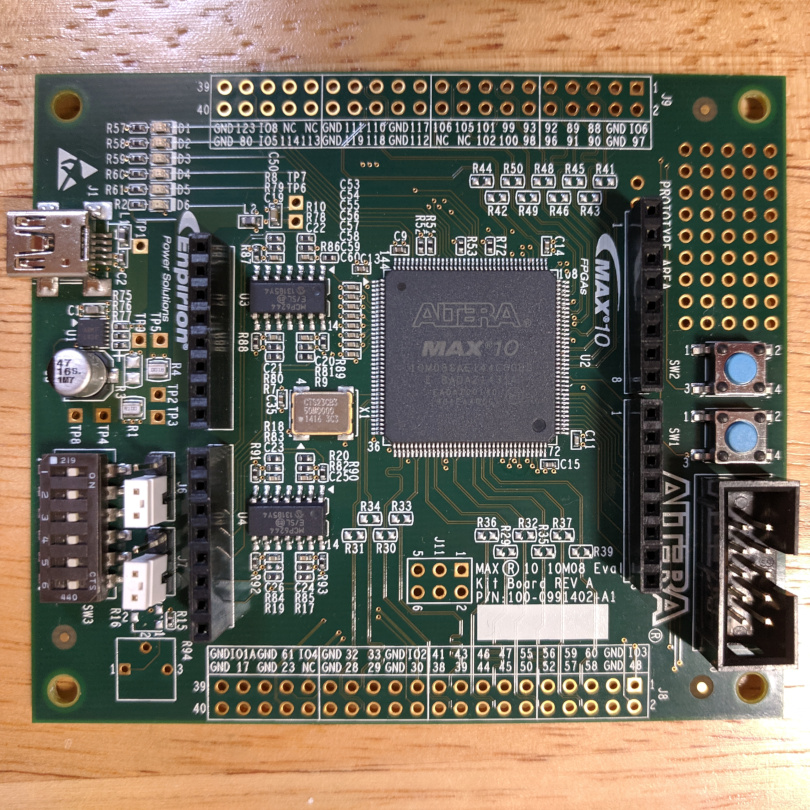

デバッグ途中でつまずいたときに「環境のせいじゃないよ」と切り分けられるように、事前にサンプルプロジェクトの「Simple Hello World」を動かしてみます。

現時点での最終目的は「ADCで温度読み取り」の続編で、CPUでADCの値を読み取って値をPCで表示すること。

温度センサICとMAX10 FPGA ADCで温度読み取り | てつふくブログ

MAX10 FPGAのADCと外付けの温度センサICを使って室温を測ってみた。Intel FPGA開発環境のADC Toolkitを使って、MAX10のADコンバータで読み取った値の確認をします。実験に使った温度ICはアナログ出力のMicrochip製MCP9700。電圧値と温度の関係も解説。

やったこと

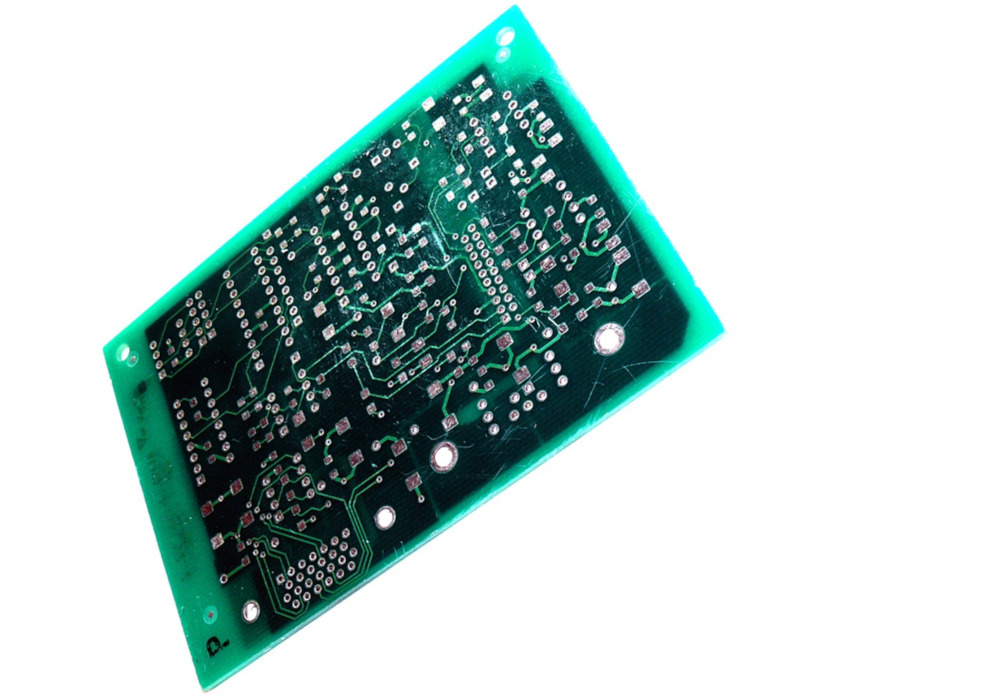

MAX10 FPGAにソフトCPUを作って、UARTでテキストを表示できることの確認。

この記事では次の内容が書いてあります。

- Platform DesignerでMAX10評価ボードにソフトCPU(Nios II)を設計して論理合成

- SDKにHW構成をエクスポート

- SDKでサンプルプロジェクトをビルドして、MAX10上で実行

1ページ目はPlatform Designerを使ってCPUを作る方法、2ページ目はSDKでの操作方法です。

設計ツール

Platform Designer

CPU周辺の構成を設計し、HDL(verilog-HDLまたはVHDL)のソースファイルを生成します。

CPUコアの設定、ペリフェラルの追加、メモリマップのアドレス割当、割り込みの設定などを行います。

また、前回ADCを動かしたときのように、CPUを使わなくても各種IPコアを接続してシステムを作ることができます。

SDK (Software Development Kit)

ソフトウェア(ファームウェア)の設計とデバッグに使うツールです。C/C++で書いた組み込みソフトウェアのビルドやデバッグをします。。

QuartusのSDKをインストールするには、eclipseを別途ダウンロードするなど追加手順が必要でした。インストール方法の説明は別記事で作成中です。

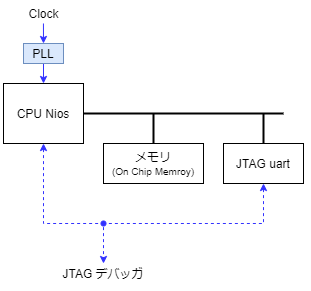

CPU構成

それでは、このブロック図の構成のCPUを作っていきます。

JTAG uartは、JTAG経由でシリアル通信ができる機能です。JTAG経由でprintfの結果が出力されることを確認しましょう。

その次の段階として、ADCの値を読み取るペリフェラルと接続し、ソフトウェアで電圧値を読めるようにする予定です。

ペリフェラルとは周辺機能のことです。通常のマイコンでは、使いたいペリフェラル搭載されているデバイスを選定しますが、このようにFPGAの中にCPUを論理合成する手法では必要なペリフェラルを選んで実装することができます。

Platform Designerの設定

Platform Designerの使用方法はADCで内部温度を読んだ記事もご覧ください。

今回追加するモジュールはこちら↓

- Clock Source (デフォルトで配置済み)

- Nios II Processor

- On-Chip Memory

- JTAG UART

- ALTPLL

IP設定

各モジュールの設定です。

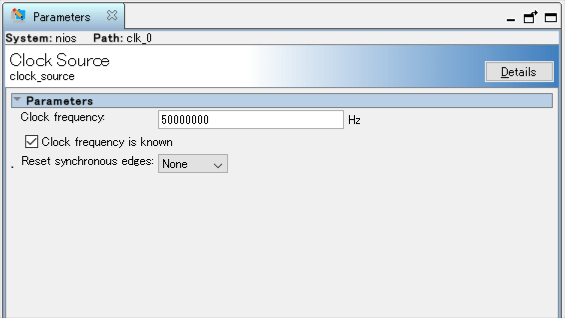

Clock Source

入力クロックの周波数は50 MHzです。

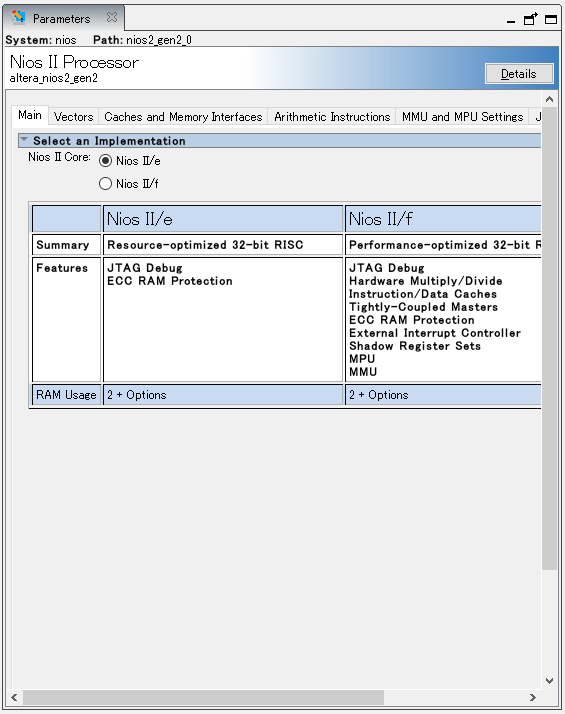

Nios II Processor

Nios II/eを選択。

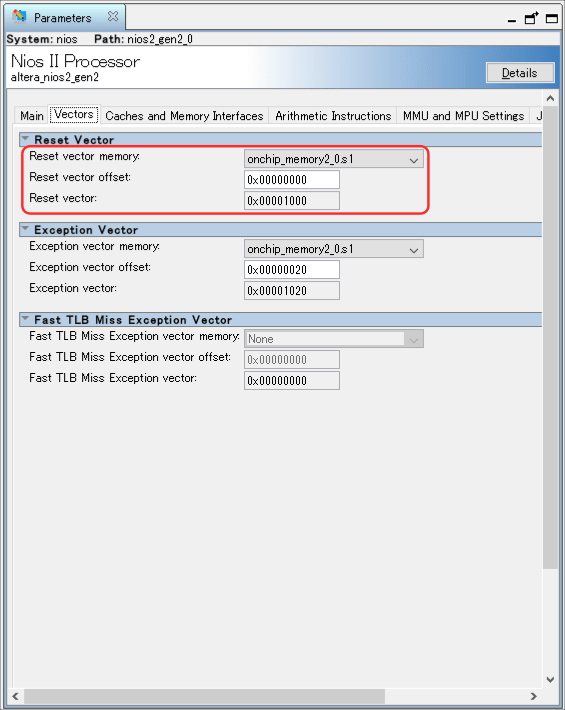

VectorsタブのReset vector memoryがOn-Chip Memoryになっていることを確認。 Reset vectorのオフセットが0、アドレスがOn-Chip Memoryの先頭アドレスになっていることを確認します。(On-Chip Memoryのアドレスは、Platform DesignerのAddress Mapタブで確認。)

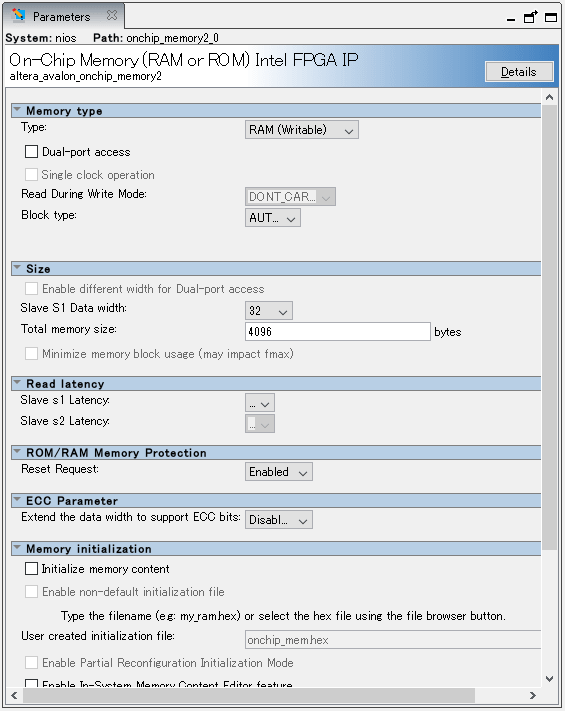

On-Chip Memory

デフォルトのまま。

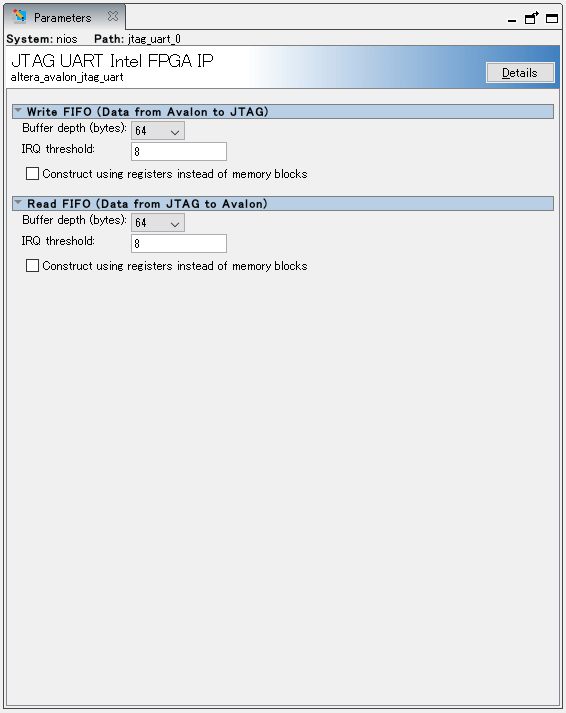

JTAG UART

デフォルトのまま。

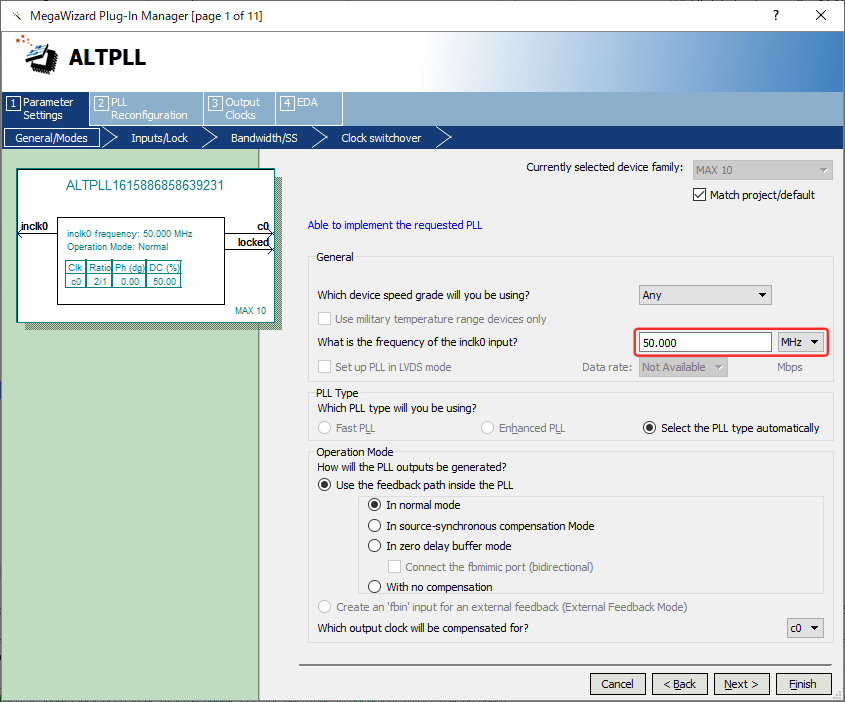

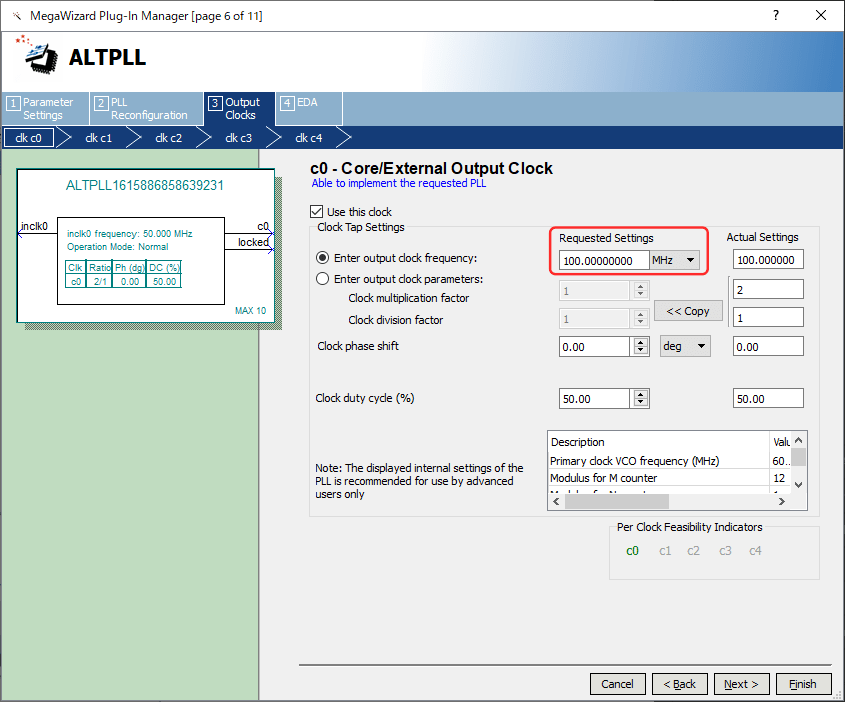

ALTPLL

入力クロックは50 MHz。

出力クロックは100 MHzに設定。

モジュール間接続

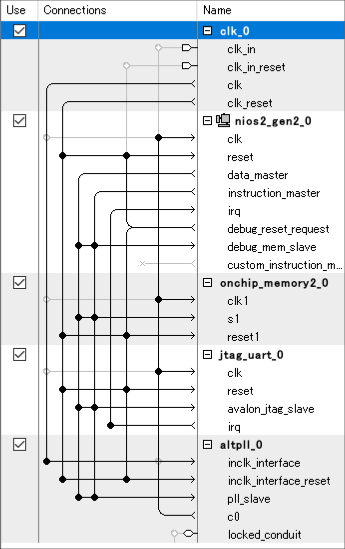

下の図のように各モジュールのクロック、リセット、データを接続します。手順などは以前の記事をご覧ください。

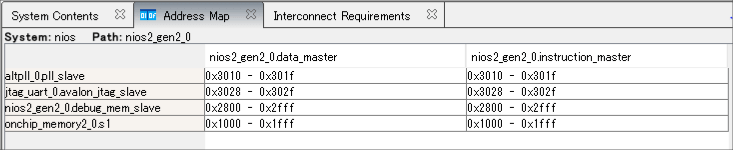

アドレス設定

アドレスタブで各ペリフェラル(モジュール)のアドレスを確認できます。

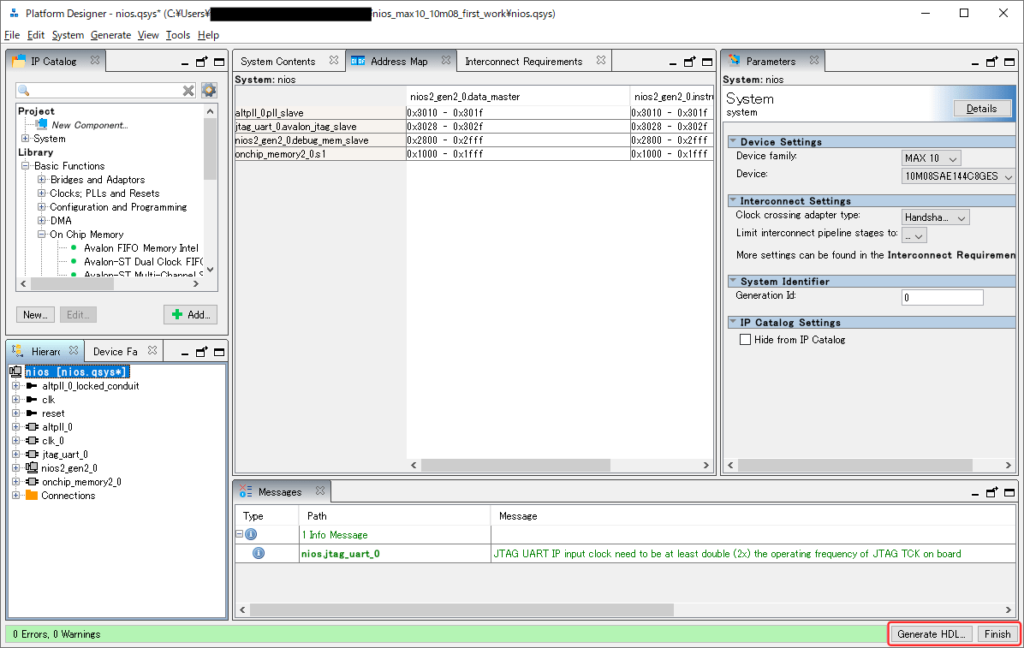

HDL生成・コンパイル

右下の”Generate HDL”ボタンをクリックしてHDL生成をスタート。

完了したら”Finish”ボタンを押してPlatform Designerを閉じましょう。(開いたままでもOKですが。)

その後、Quartus Primeに戻ってデザインのコンパイルを行います。IOやタイミングの制約も適宜。詳しい手順は別記事で。

SDK

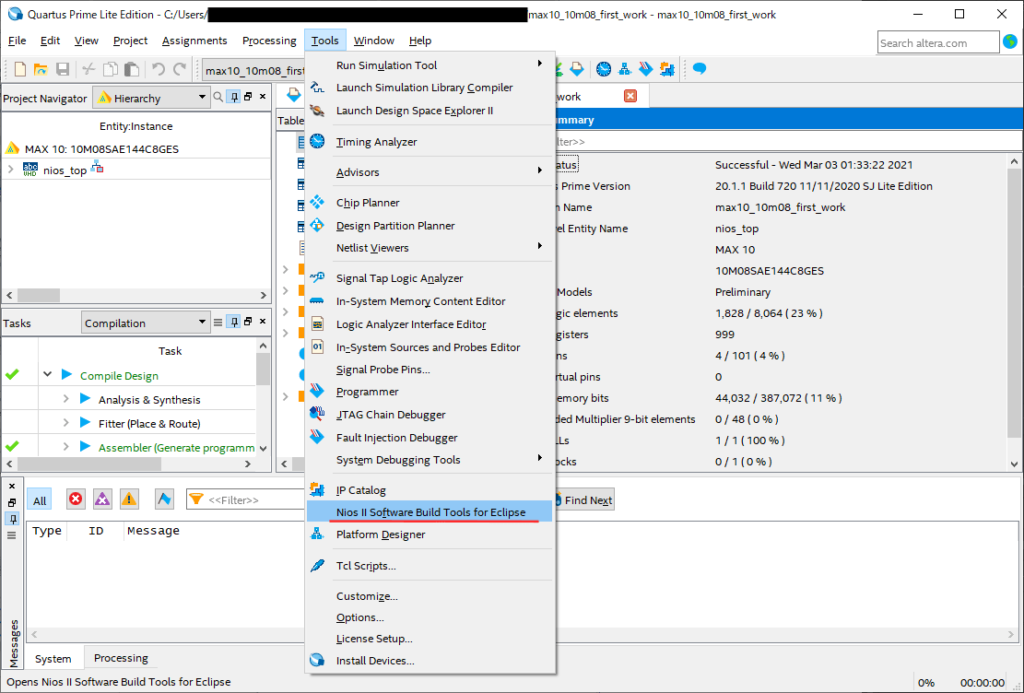

SDKを起動

コンパイルが正常に終了したら、次はソフトを書いていきます。Quartus PrimeのメニューからSDKを起動しましょう。(Quartus Primeをインストールしただけでは、SDKはインストールされません。別途インストールする必要があります。方法は改めて記事にします。)

Tools → Nios II Software Build Tools for Eclipse をクリック。

SDK起動中↓

コメントを残す